#### **Data Sheet**

# LH7A400 32-Bit System-on-Chip

#### **FEATURES**

- ARM922T<sup>™</sup> Core:

- 32-bit ARM9TDMI™ RISC Core (200 MHz)

- 16KB Cache: 8KB Instruction Cache and 8KB Data Cache

- MMU (Windows CE<sup>™</sup> Enabled)

- 80KB On-Chip Memory

- Programmable Interrupt Controller

- · External Bus Interface

- 100 MHz

- Asynchronous SRAM/ROM/Flash

- Synchronous DRAM/Flash

- PCMCIA

- CompactFlash

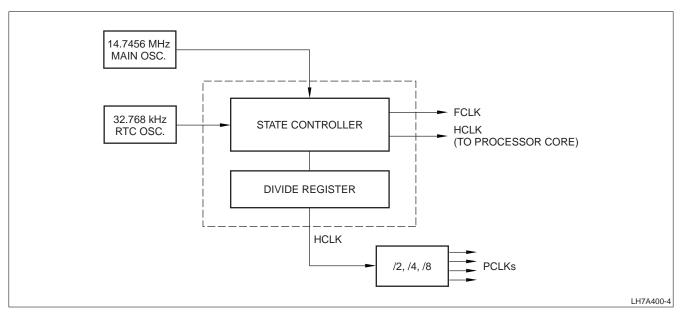

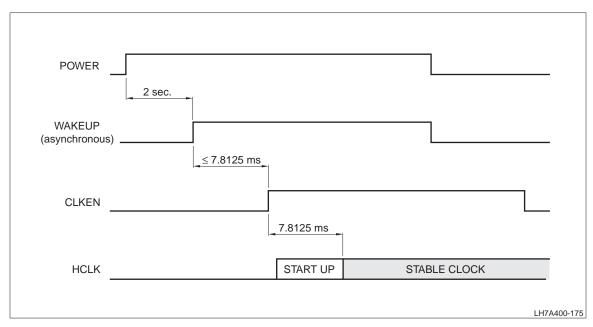

- Clock and Power Management

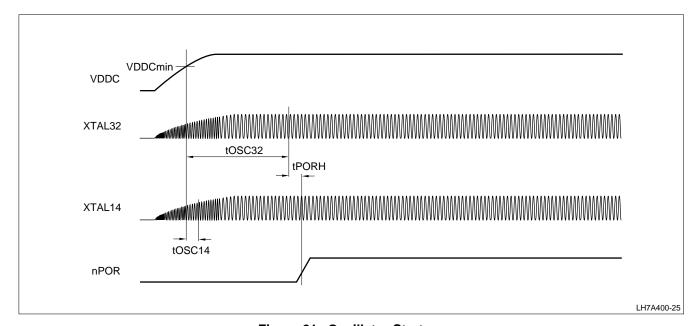

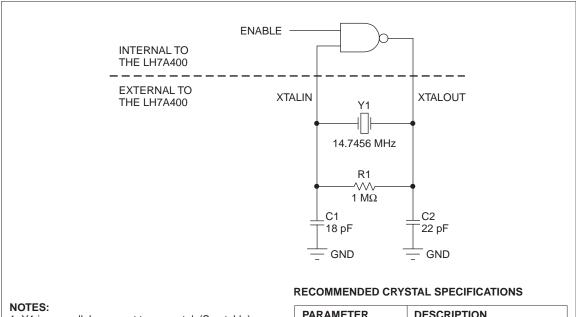

- 32.768 kHz and 14.7456 MHz Oscillators

- Programmable PLL

- · Low Power Modes (Typical)

- Run (125 mA), Halt (25 mA), Standby (42 μA)

- Programmable LCD Controller

- Up to 1,024 x 768 Resolution

- Supports STN, Color STN, AD-TFT, HR-TFT, TFT

- Up to 64 k-Colors and 15 Gray Shades

- DMA (10 Channels)

- AC97

- MMC

- USB

- USB Device Interface (USB 1.1)

- Synchronous Serial Port (SSP)

- Motorola SPI™

- Texas Instruments SSI

- National MICROWIRE™

- Three Programmable Timers

- Three UARTs

- Classic IrDA (115 kbit/s)

- Smart Card Interface (ISO7816)

- Two DC-to-DC Converters

- MultiMediaCard™ Interface

- AC97 Codec Interface

- Smart Battery Monitor Interface

- Real Time Clock (RTC)

- Up to 60 General Purpose I/Os

- · Watchdog Timer

- JTAG Debug Interface and Boundary Scan

- · Operating Voltage

- 1.8 V Core

- 3.3 V Input/Output

- 5 V Tolerant Digital Inputs (except oscillator pins)

- Oscillator pins P15, P16, R13, and T13 are 1.8 V ± 10%.

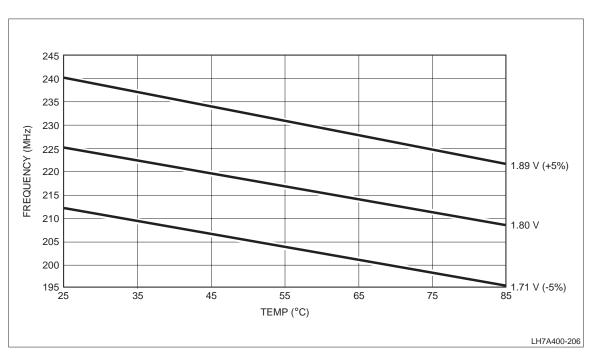

- Operating Temperature

- 0°C to +70°C Commercial

- -40°C to +85°C Industrial (With Clock Frequency Reduction)

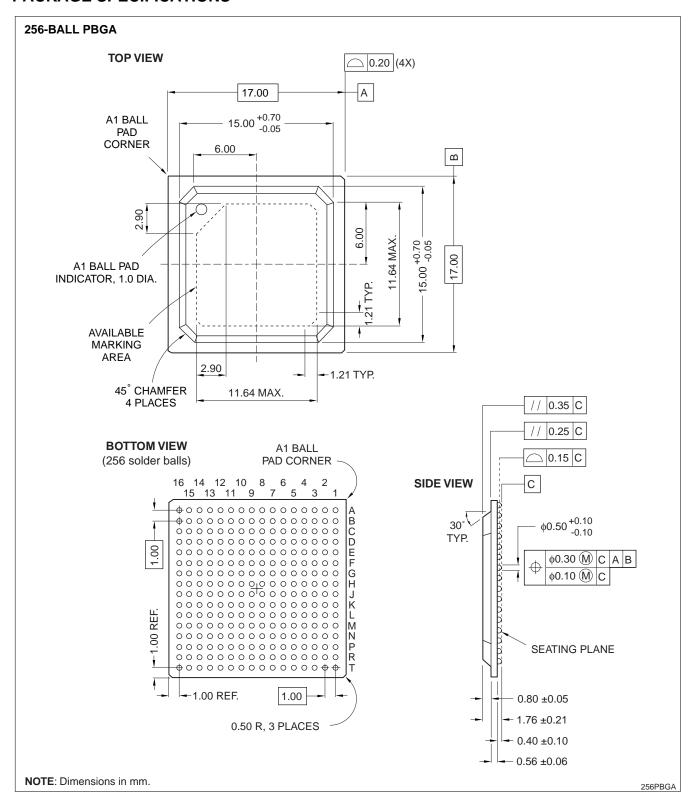

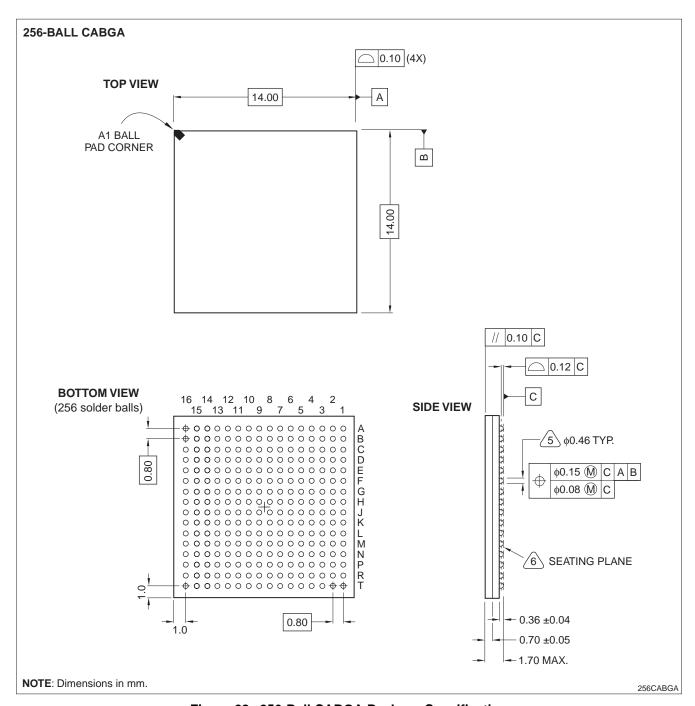

- · 256-Ball PBGA or 256-Ball CABGA Package

#### DESCRIPTION

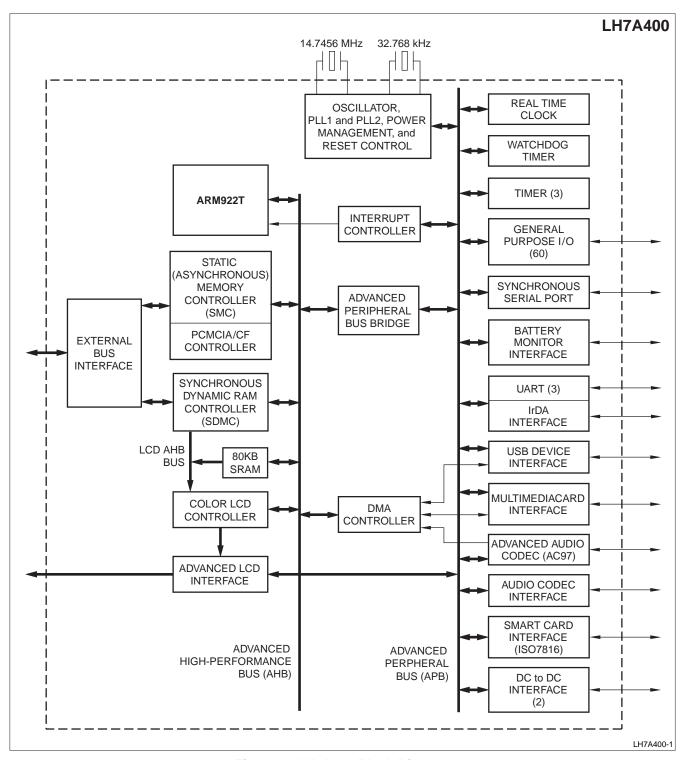

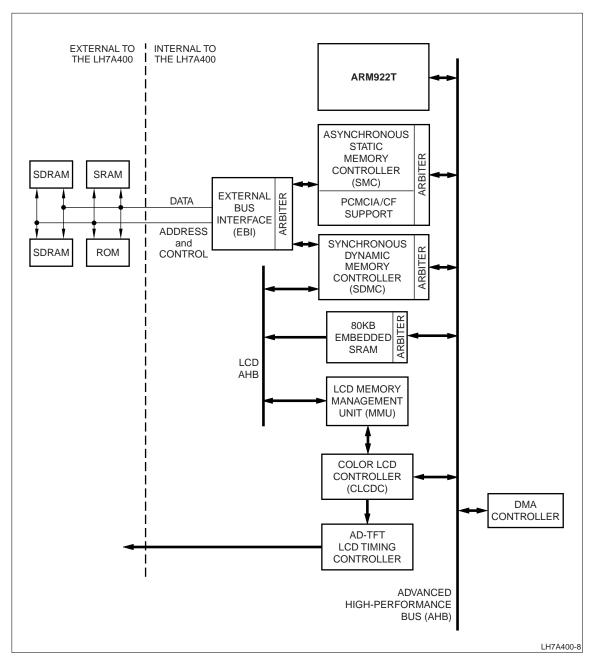

The LH7A400, powered by an ARM922T, is a complete System-on-Chip with a high level of integration to satisfy a wide range of requirements and expectations.

This high degree of integration lowers overall system costs, reduces development cycle time and accelerates product introduction.

Figure 1. LH7A400 Block Diagram

**Table 1. Functional Pin List**

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL | DESCRIPTION     | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE |

|-------------|--------------|--------|-----------------|----------------|------------------|-----------------|

| G7          | C10          |        |                 |                |                  |                 |

| F1          | F9           |        |                 |                |                  |                 |

| K7          | F11          |        |                 |                |                  |                 |

| M1          | F14          |        |                 |                |                  |                 |

| M5          | G8           |        |                 |                |                  |                 |

| T6          | H13          |        |                 |                |                  |                 |

| R14         | J9           |        |                 |                |                  |                 |

| M14         | K15          | VDD    | I/O Ring Power  |                |                  |                 |

| J11         | L7           |        |                 |                |                  |                 |

| J12         | N6           |        |                 |                |                  |                 |

| F13         | N8           |        |                 |                |                  |                 |

| B14         | N12          |        |                 |                |                  |                 |

| E10         | N13          |        |                 |                |                  |                 |

| B8          | P11          |        |                 |                |                  |                 |

| H7          | B8           |        |                 |                |                  |                 |

| G3          | C6           |        |                 |                |                  |                 |

| K4          | D5           |        |                 |                |                  |                 |

| N5          | D13          |        |                 |                |                  |                 |

| P6          | E8           |        |                 |                |                  |                 |

| T14         | F7           |        |                 |                |                  |                 |

| R16         | G13          |        |                 |                |                  |                 |

| N16         | H9           | VSS    | I/O Ring Ground |                |                  |                 |

| K13         | J14          |        |                 |                |                  |                 |

| H9          | K7           |        |                 |                |                  |                 |

| C15         | L8           |        |                 |                |                  |                 |

| A11         | L10          |        |                 |                |                  |                 |

| E8          | L12          |        |                 |                |                  |                 |

| A5          | M11          |        |                 |                |                  |                 |

| F7          | M14          |        |                 |                |                  |                 |

| E1          | C4           |        |                 |                |                  |                 |

| J4          | D7           |        |                 |                |                  |                 |

| P3          | D10          |        |                 |                |                  |                 |

| T8          | F4           |        |                 |                |                  |                 |

| K9          | F10          | VDDC   | Core Power      |                |                  |                 |

| L13         | J4           |        |                 |                |                  |                 |

| E15         | J8           |        |                 |                |                  |                 |

| D12         | K8           |        |                 |                |                  |                 |

| A7          | L6           |        |                 |                |                  |                 |

| H5          | G7           |        |                 |                |                  |                 |

| М3          | H4           |        |                 |                |                  |                 |

| L9          | H8           |        |                 |                |                  |                 |

| T10         | L4           |        |                 |                |                  |                 |

| N15         | L9           | VSSC   | Core Ground     |                |                  |                 |

| H12         | N3           |        |                 |                |                  |                 |

| B15         | N7           |        |                 |                |                  |                 |

| C9          | N10          |        |                 |                |                  |                 |

| G6          | R5           |        |                 |                |                  |                 |

Table 1. Functional Pin List (Cont'd)

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL            | DESCRIPTION                                                                                    | RESET<br>STATE  | STANDBY<br>STATE | OUTPUT<br>DRIVE |

|-------------|--------------|-------------------|------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|

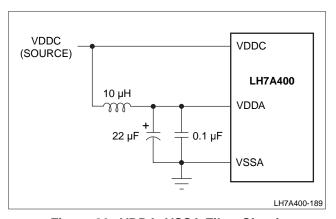

| R11         | P12          | VDDA              | Analog Power for PLL                                                                           |                 |                  |                 |

| N12         | M10          | VDDA              | Alialog Powel for PLL                                                                          |                 |                  |                 |

| P12         | R13          | VSSA              | Analog Ground for PLL                                                                          |                 |                  |                 |

| T11         | N11          | VOOA              | Alialog Ground for FEE                                                                         |                 |                  |                 |

| D3          | E4           | nPOR              | Power On Reset                                                                                 | Input           | Input            |                 |

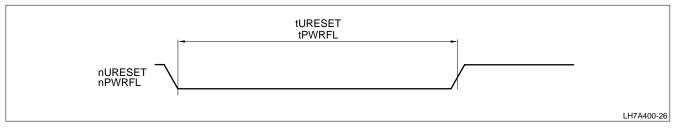

| H6          | D1           | nURESET           | User Reset; should be pulled HIGH for normal or JTAG operation.                                | Input (Schmitt) | Input            |                 |

| D4          | E2           | WAKEUP            | Wake Up                                                                                        | Input (Schmitt) | Input            |                 |

| E4          | F2           | nPWRFL            | Power Fail Signal                                                                              | Input (Schmitt) | Input            |                 |

| C2          | D2           | nEXTPWR           | External Power                                                                                 | Input (Schmitt) | Input            |                 |

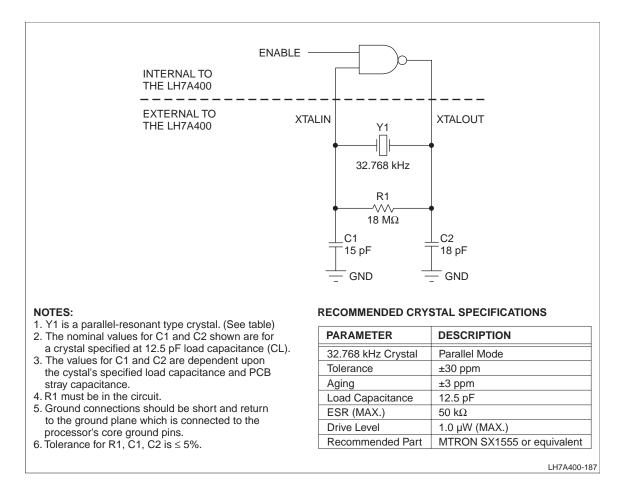

| R13         | R14          | XTALIN            | 14.7456 MHz Crystal Oscillator pins. An external clock source can be connected to XTALIN leav- | Input           | Input            |                 |

| T13         | R15          | XTALOUT           | ing XTALOUT open.                                                                              | LOW             | LOW              |                 |

| P16         | N14          | XTAL32IN          | 32.768 kHz Real Time Clock Crystal Oscillator pins. An external clock source can be connected  | Input           | Input            |                 |

| P15         | M13          | XTAL32OUT         | to XTAL32IN leaving XTAL32OUT open.                                                            | Output          | Output           |                 |

| P14         | M12          | CLKEN             | External Oscillator Clock Enable Output                                                        | LOW             | LOW              | 8 mA            |

| J6          | J5           | PGMCLK            | Programmable Clock (14.7456 MHz MAX.)                                                          | LOW             | LOW              | 8 mA            |

| K11         | P14          | nCS0              | Asynchronous Memory Chip Select 0                                                              | HIGH            | HIGH             | 12 mA           |

| K10         | P16          | nCS1              | Asynchronous Memory Chip Select 1                                                              | HIGH            | HIGH             | 12 mA           |

| P13         | N15          | nCS2              | Asynchronous Memory Chip Select 2                                                              | HIGH            | HIGH             | 12 mA           |

| M12         | N16          | nCS3/<br>nMMSPICS | Asynchronous Memory Chip Select 3     MultiMediaCard SPI Mode Chip Select                      | HIGH: nCS3      | HIGH             | 12 mA           |

Table 1. Functional Pin List (Cont'd)

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL  | DESCRIPTION                                                          | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE |

|-------------|--------------|---------|----------------------------------------------------------------------|----------------|------------------|-----------------|

| L12         | L11          | D0      |                                                                      |                |                  |                 |

| M15         | L13          | D1      |                                                                      |                |                  |                 |

| N13         | L14          | D2      |                                                                      |                |                  |                 |

| L16         | K11          | D3      |                                                                      |                |                  |                 |

| L15         | L16          | D4      |                                                                      |                |                  |                 |

| L14         | K14          | D5      |                                                                      |                |                  |                 |

| H11         | J15          | D6      |                                                                      |                |                  |                 |

| K12         | J12          | D7      |                                                                      |                |                  |                 |

| J15         | J10          | D8      |                                                                      |                |                  |                 |

| J13         | H16          | D9      |                                                                      |                |                  |                 |

| J10         | H14          | D10     |                                                                      |                |                  |                 |

| H15         | H11          | D11     |                                                                      |                |                  |                 |

| H13         | G16          | D12     |                                                                      |                |                  |                 |

| G15         | G9           | D13     |                                                                      |                |                  |                 |

| G11         | G14          | D14     |                                                                      |                |                  |                 |

| G12         | G12          | D15     | Data Bus                                                             | LOW            | LOW              | 12 mA           |

| F15         | F15          | D16     | - Data Bus                                                           | LOW            | LOW              | 1211114         |

| F12         | E15          | D17     |                                                                      |                |                  |                 |

| E14         | D16          | D18     |                                                                      |                |                  |                 |

| D16         | F12          | D19     |                                                                      |                |                  |                 |

| H10         | E13          | D20     |                                                                      |                |                  |                 |

| D14         | D14          | D21     |                                                                      |                |                  |                 |

| F10         | E12          | D22     |                                                                      |                |                  |                 |

| A16         | B16          | D23     |                                                                      |                |                  |                 |

| A14         | D12          | D24     |                                                                      |                |                  |                 |

| B13         | A16          | D25     |                                                                      |                |                  |                 |

| C13         | B13          | D26     |                                                                      |                |                  |                 |

| E12         | B14          | D27     |                                                                      |                |                  |                 |

| G10         | C12          | D28     |                                                                      |                |                  |                 |

| B12         | A14          | D29     |                                                                      |                |                  |                 |

| B11         | B12          | D30     |                                                                      |                |                  |                 |

| D11         | A12          | D31     |                                                                      |                |                  |                 |

| M16         | M15          | A0/nWE1 | Asynchronous Address Bus     Asynchronous Memory Write Byte Enable 1 | HIGH: nWE1     | HIGH             | 12 mA           |

| N14         | M16          | A1/nWE2 | Asynchronous Address Bus     Asynchronous Memory Write Byte Enable 2 | HIGH: nWE2     | HIGH             | 12 mA           |

Table 1. Functional Pin List (Cont'd)

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL      | DESCRIPTION                                                                                        | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE                      |

|-------------|--------------|-------------|----------------------------------------------------------------------------------------------------|----------------|------------------|--------------------------------------|

| M13         | L15          | A2/SA0      |                                                                                                    | LOW            | LOW              | 12 mA                                |

| K16         | K12          | A3/SA1      |                                                                                                    | LOW            | LOW              | 12 mA                                |

| K15         | K13          | A4/SA2      |                                                                                                    | LOW            | LOW              | 12 mA                                |

| K14         | K16          | A5/SA3      |                                                                                                    | LOW            | LOW              | 12 mA                                |

| J8          | J13          | A6/SA4      |                                                                                                    | LOW            | LOW              | 12 mA                                |

| J16         | J11          | A7/SA5      |                                                                                                    | LOW            | LOW              | 12 mA                                |

| J14         | J16          | A8/SA6      | Asynchronous Address Bus                                                                           | LOW            | LOW              | 12 mA                                |

| J9          | H15          | A9/SA7      | Synchronous Address Bus                                                                            | LOW            | LOW              | 12 mA                                |

| H16         | H10          | A10/SA8     |                                                                                                    | LOW            | LOW              | 12 mA                                |

| H14         | H12          | A11/SA9     |                                                                                                    | LOW            | LOW              | 12 mA                                |

| G16         | G15          | A12/SA10    |                                                                                                    | LOW            | LOW              | 12 mA                                |

| G14         | G10          | A13/SA11    |                                                                                                    | LOW            | LOW              | 12 mA                                |

| G13         | G11          | A14/SA12    |                                                                                                    | LOW            | LOW              | 12 mA                                |

| F16         | F16          | A15/SA13    |                                                                                                    | LOW            | LOW              | 12 mA                                |

| F14         | E16          | A16/SB0     | Asynchronous Address Bus     Synchronous Device Bank Address 0                                     | LOW            | LOW              | 12 mA                                |

| E16         | F13          | A17/SB1     | Asynchronous Address Bus     Synchronous Device Bank Address 1                                     | LOW            | LOW              | 12 mA                                |

| E13         | E14          | A18         |                                                                                                    |                |                  |                                      |

| F11         | D15          | A19         |                                                                                                    |                |                  |                                      |

| D15         | C16          | A20         |                                                                                                    |                |                  |                                      |

| C16         | C15          | A21         | Asynchronous Address Bus                                                                           | LOW            | LOW              | 12 mA                                |

| B16         | C14          | A22         |                                                                                                    |                |                  |                                      |

| A15         | B15          | A23         |                                                                                                    |                |                  |                                      |

| A13         | E11          | A24         |                                                                                                    |                |                  |                                      |

| G8          | D8           | A25/SCIO    | Asynchronous Memory Address Bus     Smart Card Interface I/O (Data)                                | LOW: A25       | LOW              | 12 mA                                |

| F8          | В7           | A26/SCCLK   | Asynchronous Memory Address Bus     Smart Card Interface Clock                                     | LOW: A26       | LOW              | 12 mA                                |

| A8          | A7           | A27/SCRST   | Asynchronous Memory Address Bus     Smart Card Interface Reset                                     | LOW: A27       | LOW              | 12 mA                                |

| D8          | C8           | nOE         | Asynchronous Memory Output Enable                                                                  | HIGH           | HIGH             | 12 mA                                |

| C8          | F8           | nWE0        | Asynchronous Memory Write Byte Enable 0                                                            | HIGH           | HIGH             | 12 mA                                |

| D10         | D9           | nWE3        | Asynchronous Memory Write Byte Enable 3                                                            | HIGH           | HIGH             | 8 mA                                 |

| B10         | E9           | CS6/SCKE1_2 | <ul><li>Asynchronous Memory Chip Select 6</li><li>Synchronous Memory Clock Enable 1 OR 2</li></ul> | LOW: CS6       | LOW              | 12 mA                                |

| C10         | A10          | CS7/SCKE0   | Asynchronous Memory Chip Select 7     Synchronous Memory Clock Enable 0                            | LOW: CS7       | LOW              | 12 mA                                |

| G9          | A11          | SCKE3       | Synchronous Memory Clock Enable 3                                                                  | LOW            | LOW              | 12 mA                                |

| A10         | B10          | SCLK        | Synchronous Memory Clock                                                                           | LOW            | LOW              | 20 mA<br>(sink)<br>12 mA<br>(source) |

| C14         | C13          | nSCS0       | Synchronous Memory Chip Select 0                                                                   | HIGH           | HIGH             | 12 mA                                |

| D13         | A15          | nSCS1       | Synchronous Memory Chip Select 1                                                                   | HIGH           | HIGH             | 12 mA                                |

| E11         | D11          | nSCS2       | Synchronous Memory Chip Select 2                                                                   | HIGH           | HIGH             | 12 mA                                |

| A12         | E10          | nSCS3       | Synchronous Memory Chip Select 3                                                                   | HIGH           | HIGH             | 12 mA                                |

| C12         | A13          | nSWE        | Synchronous Memory Write Enable                                                                    | HIGH           | HIGH             | 12 mA                                |

| C11         | B11          | nCAS        | Synchronous Memory Column Address<br>Strobe Signal                                                 | HIGH           | HIGH             | 12 mA                                |

Table 1. Functional Pin List (Cont'd)

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL            | DESCRIPTION                                                              | RESET<br>STATE | STANDBY<br>STATE                                         | OUTPUT<br>DRIVE |

|-------------|--------------|-------------------|--------------------------------------------------------------------------|----------------|----------------------------------------------------------|-----------------|

| F9          | C11          | nRAS              | Synchronous Memory Row Address Strobe Signal                             | HIGH           | HIGH                                                     | 12 mA           |

| A9          | C9           | DQM0              | Synchronous Memory Data Mask 0                                           | HIGH           | HIGH                                                     | 12 mA           |

| В9          | A9           | DQM1              | Synchronous Memory Data Mask 1                                           | HIGH           | HIGH                                                     | 12 mA           |

| D9          | В9           | DQM2              | Synchronous Memory Data Mask 2                                           | HIGH           | HIGH                                                     | 12 mA           |

| E9          | A8           | DQM3              | Synchronous Memory Data Mask 3                                           | HIGH           | HIGH                                                     | 12 mA           |

| J5          | K1           | PA0/LCDVD16       | GPIO Port A     LCD Data bit 16. This CLCDC output signal is always LOW. | Input: PA0     | No Change                                                | 8 mA            |

| K1          | K2           | PA1/LCDVD17       | GPIO Port A     LCD Data bit 17. This CLCDC output signal is always LOW. | Input: PA1     | No Change                                                | 8 mA            |

| K2          | K3           | PA2               |                                                                          |                |                                                          |                 |

| K3          | K4           | PA3               |                                                                          |                |                                                          |                 |

| K5          | K6           | PA4               | GPIO Port A                                                              | Input          | No Change                                                | 8 mA            |

| L1          | K5           | PA5               | GFIO FOILA                                                               | Input          | No Change                                                | OTHA            |

| L2          | L1           | PA6               |                                                                          |                |                                                          |                 |

| L3          | L2           | PA7               |                                                                          |                |                                                          |                 |

| L4          | L3           | PB0/UARTRX1       | GPIO Port B     UART1 Receive Data Input                                 | Input: PB0     | No Change                                                | 8 mA            |

| L5          | M1           | PB1/UARTTX3       | GPIO Port B     UART3 Transmit Data Out                                  | Input: PB1     | LOW if<br>UART3 is<br>Enabled,<br>otherwise<br>No Change | 8 mA            |

| L7          | M2           | PB2/UARTRX3       | GPIO Port B     UART3 Receive Data In                                    | Input: PB2     | No Change                                                | 8 mA            |

| M2          | МЗ           | PB3/<br>UARTCTS3  | GPIO Port B     UART3 Clear to Send                                      | Input: PB3     | No Change                                                | 8 mA            |

| M4          | L5           | PB4/<br>UARTDCD3  | GPIO Port B     UART3 Data Carrier Detect                                | Input: PB4     | No Change                                                | 8 mA            |

| N1          | N1           | PB5/<br>UARTDSR3  | GPIO Port B     UART3 Data Set Ready                                     | Input: PB5     | No Change                                                | 8 mA            |

| N2          | N2           | PB6/SWID/<br>SMBD | GPIO Port B     Single Wire Data     Smart Battery Data                  | Input: PB6     | Input if SMB is Enabled, otherwise No Change             | 8 mA            |

| N3          | M4           | PB7/SMBCLK        | GPIO Port B     Smart Battery Clock                                      | Input: PB7     | Input if SMB is Enabled, otherwise No Change             | 8 mA            |

| P1          | P1           | PC0/UARTTX1       | GPIO Port C     UART1 Transmit Data Output                               | LOW: PC0       | No Change                                                | 12 mA           |

| P2          | P2           | PC1/LCDPS         | GPIO Port C     HR-TFT Power Save                                        | LOW: PC1       | No Change                                                | 12 mA           |

| R1          | R1           | PC2/<br>LCDVDDEN  | GPIO Port C     HR-TFT Power Sequence Control                            | LOW: PC2       | No Change                                                | 12 mA           |

| K6          | M5           | PC3/LCDREV        | GPIO Port C     HR-TFT Gray Scale Voltage Reverse                        | LOW: PC3       | No Change                                                | 12 mA           |

| L8          | P3           | PC4/LCDSPS        | GPIO Port C     HR-TFT Reset Row Driver Counter                          | LOW: PC4       | No Change                                                | 12 mA           |

| T1          | N4           | PC5/LCDCLS        | GPIO Port C     HR-TFT Row Driver Clock                                  | LOW: PC5       | No Change                                                | 12 mA           |

Table 1. Functional Pin List (Cont'd)

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL                | DESCRIPTION                                                                                                                                                                                           | RESET<br>STATE          | STANDBY<br>STATE                                     | OUTPUT<br>DRIVE |

|-------------|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------|-----------------|

| T2          | R2           | PC6/LCDHRLP           | GPIO Port C     LCD Latch Pulse                                                                                                                                                                       | LOW: PC6                | No Change                                            | 12 mA           |

| R2          | N5           | PC7/LCDSPL            | GPIO Port C     LCD Start Pulse Left                                                                                                                                                                  | LOW: PC7                | No Change                                            | 12 mA           |

| M11         | M9           | PD0/LCDVD8            |                                                                                                                                                                                                       | LOW: PD0                |                                                      |                 |

| L11         | K10          | PD1/LCDVD9            |                                                                                                                                                                                                       | LOW: PD1                | LOW if                                               |                 |

| K8          | P10          | PD2/LCDVD10           |                                                                                                                                                                                                       | LOW: PD2                | Dual-Panel                                           |                 |

| N11         | T11          | PD3/LCDVD11           | GPIO Port D                                                                                                                                                                                           | LOW: PD3                | LCD is                                               | 12 mA           |

| R9          | T12          | PD4/LCDVD12           | LCD Video Data Bus                                                                                                                                                                                    | LOW: PD4                | Enabled;                                             | 12111/4         |

| T9          | R11          | PD5/LCDVD13           |                                                                                                                                                                                                       | LOW: PD5                | otherwise,                                           |                 |

| P10         | R12          | PD6/LCDVD14           |                                                                                                                                                                                                       | LOW: PD6                | No Change                                            |                 |

| R10         | T13          | PD7/LCDVD15           |                                                                                                                                                                                                       | LOW: PD7                |                                                      |                 |

| L10         | T9           | PE0/LCDVD4            |                                                                                                                                                                                                       | Input: PE0              | LOW if 8-bit                                         |                 |

| N10         | K9           | PE1/LCDVD5            | GPIO Port E                                                                                                                                                                                           | Input: PE1              | LCD is                                               |                 |

| M9          | T10          | PE2/LCDVD6            | LCD Video Data Bus                                                                                                                                                                                    | Input: PE2              | Enabled,                                             | 12 mA           |

| M10         | R10          | PE3/LCDVD7            |                                                                                                                                                                                                       | Input: PE3              | otherwise<br>No Change                               |                 |

| A6          | A5           | PF0/INT0              | <ul> <li>GPIO Port F</li> <li>External FIQ Interrupt. Interrupts can be level or<br/>edge triggered and are internally debounced.</li> </ul>                                                          | Input: PF0<br>(Schmitt) | No Change                                            | 8 mA            |

| В6          | B4           | PF1/INT1              | GPIO Port F     External IRQ Interrupts. Interrupts can be level                                                                                                                                      | Input: PF1<br>(Schmitt) | No Change                                            | 8 mA            |

| C6          | E7           | PF2/INT2              | or edge triggered and are internally debounced.                                                                                                                                                       | Input: PF2<br>(Schmitt) | No Change                                            | 8 mA            |

| H8          | ВЗ           | PF3/INT3              | GPIO Port F     External IRQ Interrupt. Interrupts can be level or edge triggered and are internally debounced.                                                                                       | Input: PF3<br>(Schmitt) | No Change                                            | 8 mA            |

| B5          | C5           | PF4/INT4/<br>SCVCCEN  | GPIO Port F     External IRQ Interrupt. Interrupts can be level or edge triggered and are internally debounced.     Smart Card Supply Voltage Enable                                                  | Input: PF4<br>(Schmitt) | LOW if SCI<br>is Enabled;<br>otherwise,<br>No Change | 8 mA            |

| D6          | D6           | PF5/INT5/<br>SCDETECT | <ul> <li>GPIO Port F</li> <li>External IRQ Interrupt. Interrupts can be level or<br/>edge triggered and are internally debounced.</li> <li>Smart Card Detection</li> </ul>                            | Input: PF5<br>(Schmitt) | No Change                                            | 8 mA            |

| E6          | A4           | PF6/INT6/<br>PCRDY1   | GPIO Port F     External IRQ Interrupt. Interrupts can be level or edge triggered and are internally debounced.     Ready for Card 1 for PC Card (PCMCIA or CompactFlash) in single or dual card mode | Input: PF6<br>(Schmitt) | No Change                                            | 8 mA            |

| C5          | А3           | PF7/INT7/<br>PCRDY2   | GPIO Port F     External IRQ Interrupt. Interrupts can be level or Input: PE7                                                                                                                         |                         | No Change                                            | 8 mA            |

| R3          | M6           | PG0/nPCOE             | GPIO Port G     Output Enable for PC Card (PCMCIA or CompactFlash) in single or dual card mode                                                                                                        | LOW: PG0                | No Change                                            | 8 mA            |

| Т3          | T1           | PG1/nPCWE             | GPIO Port G     Write Enable for PC Card (PCMCIA or CompactFlash) in single or dual card mode                                                                                                         | LOW: PG1                | No Change                                            | 8 mA            |

Table 1. Functional Pin List (Cont'd)

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL                               | DESCRIPTION                                                                                                                                                                                                                                                                                         | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE |

|-------------|--------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|

| L6          | P4           | PG2/nPCIOR                           | GPIO Port G     I/O Read Strobe for PC Card (PCMCIA or CompactFlash) in single or dual card mode                                                                                                                                                                                                    | LOW: PG2       | No Change        | 8 mA            |

| M6          | R3           | PG3/nPCIOW                           | GPIO Port G     I/O Write Strobe for PC Card (PCMCIA or CompactFlash) in single or dual card mode                                                                                                                                                                                                   | LOW: PG3       | No Change        | 8 mA            |

| N6          | T2           | PG4/nPCREG                           | GPIO Port G     Register Memory Access for PC Card (PCMCIA or CompactFlash) in single or dual card mode                                                                                                                                                                                             | LOW: PG4       | No Change        | 8 mA            |

| M7          | P5           | PG5/nPCCE1                           | GPIO Port G     Card Enable 1 for PC Card (PCMCIA or CompactFlash) in single or dual card mode. This signal and nPCCE2 are used by the PC Card for decoding low and high byte accesses.                                                                                                             | LOW: PG5       | No Change        | 8 mA            |

| M8          | R4           | PG6/nPCCE2                           | GPIO Port G     Card Enable 2 for PC Card (PCMCIA or CompactFlash) in single or dual card mode. This signal and nPCCE1 are used by the PC Card for decoding low and high byte accesses.                                                                                                             | LOW: PG6       | No Change        | 8 mA            |

| N4          | Т3           | PG7/PCDIR                            | GPIO Port G     Direction for PC Card (PCMCIA or CompactFlash) in single or dual card mode                                                                                                                                                                                                          | LOW: PG7       | No Change        | 8 mA            |

| P4          | P6           | PH0/<br>PCRESET1                     | GPIO Port H     Reset Card 1 for PC Card (PCMCIA or CompactFlash) in single or dual card mode                                                                                                                                                                                                       | Input: PH0     | No Change        | 8 mA            |

| R4          | T4           | PH1/CFA8/<br>PCRESET2                | GPIO Port H     Address Bit 8 for PC Card (CompactFlash) in single card mode     Reset Card 2 for PC Card (PCMCIA or CompactFlash) in dual card mode                                                                                                                                                | Input: PH1     | No Change        | 8 mA            |

| T4          | M7           | PH2/<br>nPCSLOTE1                    | GPIO Port H     Enable Card 1 for PC Card (PCMCIA or CompactFlash) in single or dual card mode. This signal is used for gating other control signals to the appropriate PC Card.                                                                                                                    | Input: PH2     | No Change        | 8 mA            |

| N7          | Т5           | PH3/CFA9/<br>PCMCIAA25/<br>nPCSLOTE2 | GPIO Port H     Address Bit 9 for PC Card (CompactFlash) in single card mode     Address Bit 25 for PC Card (PCMCIA) in single card mode     Enable Card 2 for PC Card (PCMCIA or CompactFlash) in dual card mode. This signal is used for gating other control signals to the appropriate PC Card. | Input: PH3     | No Change        | 8 mA            |

| P8          | R6           | PH4/<br>nPCWAIT1                     | GPIO Port H     WAIT Signal for Card 1 for PC Card (PCMCIA or CompactFlash) in single or dual card mode                                                                                                                                                                                             | Input: PH4     | No Change        | 8 mA            |

| P5          | R7           | PH5/CFA10/<br>PCMCIAA24/<br>nPCWAIT2 | GPIO Port H     Address Bit 10 for PC Card (CompactFlash) in single card mode     Address Bit 24 for PC Card (PCMCIA) in single card mode     WAIT Signal for Card 2 for PC Card (PCMCIA or CompactFlash) in dual card mode                                                                         | Input: PH5     | No Change        | 8 mA            |

Table 1. Functional Pin List (Cont'd)

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL                | DESCRIPTION                                                                                                        | RESET<br>STATE    | STANDBY<br>STATE | OUTPUT<br>DRIVE |

|-------------|--------------|-----------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|

| R5          | P7           | PH6/<br>AC97RESET     | GPIO Port H     Audio Codec (AC97) Reset                                                                           | Input: PH6        | No Change        | 8 mA            |

| T5          | T6           | PH7/nPC-<br>STATRE    | GPIO Port H     Status Read Enable for PC Card (PCMCIA or CompactFlash) in single or dual card mode                | Input: PH7        | No Change        | 8 mA            |

| R6          | T7           | LCDFP                 | LCD Frame Synchronization pulse                                                                                    | LOW               | LOW              | 12 mA           |

| R8          | R9           | LCDLP                 | LCD Line Synchronization pulse                                                                                     | LOW               | LOW              | 12 mA           |

| P9          | P9           | LCDENAB/<br>LCDM      | LCD TFT Data Enable     LCD STN AC Bias                                                                            | LOW:<br>LCDENAB   | LOW              | 12 mA           |

| N9          | N9           | LCDDCLK               | LCD Data Clock                                                                                                     | LOW               | LOW              | 12 mA           |

| P7          | M8           | LCDVD0                |                                                                                                                    |                   |                  |                 |

| R7          | P8           | LCDVD1                | LCD Video Data Bus                                                                                                 | LOW               | LOW              | 12 mA           |

| T7          | R8           | LCDVD2                |                                                                                                                    |                   |                  |                 |

| N8          | T8           | LCDVD3                |                                                                                                                    |                   |                  |                 |

| T15         | T16          | USBDP                 | USB Data Positive (Differential Pair)                                                                              | Input             | Input            | 75 mA<br>(NOM.) |

| T16         | R16          | USBDN                 | USB Data Negative (Differential Pair)                                                                              | Input             | Input            | 75 mA<br>(NOM.) |

| E7          | C7           | nPWME0                | DC-DC Converter Pulse Width<br>Modulator 0 Enable                                                                  | Input             | Input            |                 |

| D7          | A6           | nPWME1                | DC-DC Converter Pulse Width<br>Modulator 1 Enable                                                                  | Input             | Input            |                 |

| C7          | В6           | PWM0                  | DC-DC Converter Pulse Width<br>Modulator 0 Output during normal operation and<br>Polarity Selection input at reset | Input             | Input            | 8 mA            |

| B7          | B5           | PWM1                  | DC-DC Converter Pulse Width<br>Modulator 1 Output during normal operation and<br>Polarity Selection input at reset | Input             | Input            | 8 mA            |

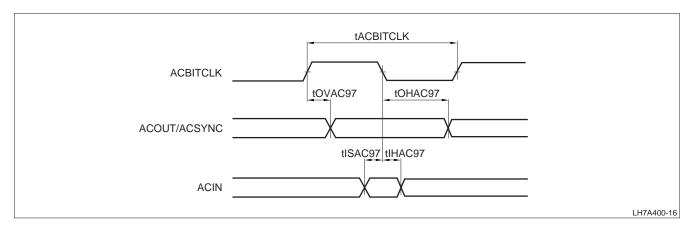

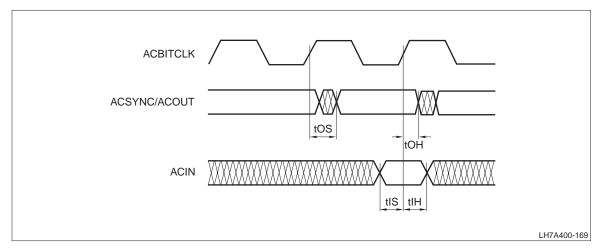

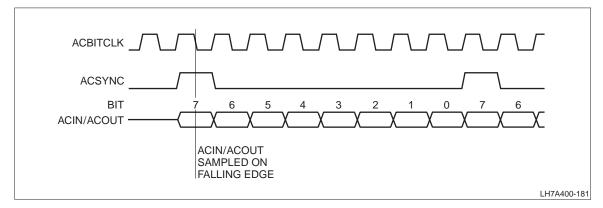

| C4          | A2           | ACBITCLK              | Audio Codec (AC97) Clock     Audio Codec (ACI) Clock                                                               | Input             | Input            |                 |

| D5          | A1           | ACOUT                 | Audio Codec (AC97) Output     Audio Codec (ACI) Output                                                             | LOW               | LOW              | 8 mA            |

| B4          | B2           | ACSYNC                | <ul><li>Audio Codec (AC97) Synchronization</li><li>Audio Codec (ACI) Synchronization</li></ul>                     | LOW               | LOW              | 8 mA            |

| A4          | E6           | ACIN                  | Audio Codec (AC97) Input     Audio Codec (ACI) Input                                                               | Input             | Input            |                 |

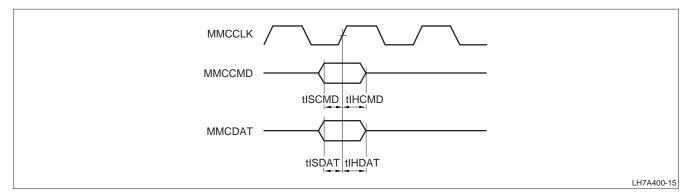

| A3          | C3           | MMCCLK/<br>MMSPICLK   | MultiMediaCard Clock (20 MHz MAX.)     MultiMediaCard SPI Mode Clock                                               | LOW:<br>MMCCLK    | LOW              | 8 mA            |

| В3          | B1           | MMCCMD/<br>MMSPIDIN   | MultiMediaCard Command     MultiMediaCard SPI Mode Data Input                                                      | Input:<br>MMCCMD  | Input            | 8 mA            |

| A2          | D4           | MMCDATA/<br>MMSPIDOUT | MultiMediaCard Data     MultiMediaCard SPI Mode Data Output                                                        | Input:<br>MMCDATA | Input            | 8 mA            |

| E2          | E1           | UARTCTS2              | UART2 Clear to Send Signal. This pin is an output for JTAG boundary scan only.                                     | Input             | Input            |                 |

| E3          | F3           | UARTDCD2              | UART2 Data Carrier Detect Signal. This pin is output for JTAG boundary scan only.                                  | Input             | Input            |                 |

| E5          | G4           | UARTDSR2              | UART2 Data Set Ready Signal                                                                                        | Input             | Input            |                 |

| F2          | G5           | UARTIRTX1             | IrDA Transmit                                                                                                      | LOW               | LOW              | 8 mA            |

| F3          | G6           | UARTIRRX1             | IrDA Receive. This pin is an output for JTAG boundary scan only.                                                   | Input             | Input            |                 |

| F4          | F1           | UARTTX2               | UART2 Transmit Data Output                                                                                         | HIGH              | HIGH             | 8 mA            |

Table 1. Functional Pin List (Cont'd)

| PBGA<br>PIN | CABGA<br>PIN | SIGNAL             | DESCRIPTION                                                                                    | RESET<br>STATE        | STANDBY<br>STATE      | OUTPUT<br>DRIVE |

|-------------|--------------|--------------------|------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------|

| J7          | G3           | UARTRX2            | UART2 Receive Data Input. This pin is an output for JTAG boundary scan only.                   | Input                 | Input                 |                 |

| H4          | J3           | SSPCLK             | Synchronous Serial Port Clock                                                                  | LOW                   | LOW                   | 8 mA            |

| J1          | J6           | SSPRX              | Synchronous Serial Port Receive                                                                | Input                 | Input                 |                 |

| J2          | J7           | SSPTX              | Synchronous Serial Port Transmit                                                               | LOW                   | LOW                   | 8 mA            |

| J3          | J2           | SSPFRM/<br>nSSPFRM | Synchronous Serial Port Frame Sync                                                             | HIGH:                 | Output                | 8 mA            |

| F6          | G2           | COL0               |                                                                                                |                       |                       |                 |

| F5          | G1           | COL1               |                                                                                                |                       |                       |                 |

| G1          | НЗ           | COL2               |                                                                                                |                       |                       |                 |

| G2          | H5           | COL3               | Keyboard Interface                                                                             | HIGH                  | HIGH                  | 8 mA            |

| G4          | H6           | COL4               | Reyboard interface                                                                             | півп                  | ПІВП                  | OIIIA           |

| G5          | H7           | COL5               |                                                                                                |                       |                       |                 |

| H1          | H2           | COL6               |                                                                                                |                       |                       |                 |

| H2          | H1           | COL7               |                                                                                                |                       |                       |                 |

| Н3          | J1           | TBUZ               | Timer Buzzer (254 kHz MAX.)                                                                    | LOW                   | LOW                   | 8 mA            |

| С3          | F5           | MEDCHG             | Boot Device Media Change. Used with WIDTH0 and WIDTH1 to specify boot memory device.           | Input (Schmitt)       | Input                 |                 |

| P11         | T14          | WIDTH0             | External Memory Width Pins. Also, used with MEDCHG to specify the boot memory device size.     | Input (Schmitt)       | Input with            |                 |

| R12         | T15          | WIDTH1             | These pins have weak internal pull-up resistors.                                               | with pull-up          | pull-up               |                 |

| D1          | E3           | BATOK              | Battery OK                                                                                     | Input (Schmitt)       | Input                 |                 |

| D2          | F6           | nBATCHG            | Battery Change                                                                                 | Input (Schmitt)       | Input                 |                 |

| A1          | E5           | TDI                | JTAG Data In. This signal is internally pulled-up to VDD.                                      | Input with<br>Pull-up | Input with<br>Pull-up |                 |

| B1          | C2           | тск                | JTAG Clock. This signal should be externally pulled-up to VDD.                                 | Input                 | Input                 |                 |

| B2          | D3           | TDO                | JTAG Data Out. This signal should be externally pulled up to VDD with a 33 $k\Omega$ resistor. | Input                 | No Change             | 4 mA            |

| C1          | C1           | TMS                | JTAG Test Mode select. This signal is internally pulled-up to VDD.                             | Input with<br>Pull-up | Input with<br>Pull-up |                 |

| T12         | P15          | nTEST0             | Test Pin 0. Internally pulled up to VDD. For Normal Input with                                 |                       | Input with<br>Pull-up |                 |

| R15         | P13          | nTEST1             | Test Pin 1. internally pulled up to VDD. For Normal and JTAG mode, leave open. See Table 2.    | Input with<br>Pull-up | Input with<br>Pull-up |                 |

NOTES: \*Signals beginning with 'n' are Active LOW.

Table 2. nTest Pin Function

| MODE   | nTEST0 | nTEST1 | nURESET |

|--------|--------|--------|---------|

| JTAG   | 0      | 1      | 1       |

| Normal | 1      | 1      | х       |

**Table 3. LCD Data Multiplexing**

|      |       |             |                 |               | ST              | N             |                 |               |           |           |

|------|-------|-------------|-----------------|---------------|-----------------|---------------|-----------------|---------------|-----------|-----------|

| PBGA | CABGA | LCD<br>DATA | MONO            | 4-BIT         | MONO            | 8-BIT         | COL             | _OR           | TFT       | AD-TFT/   |

| PIN  | PIN   | SIGNAL      | SINGLE<br>PANEL | DUAL<br>PANEL | SINGLE<br>PANEL | DUAL<br>PANEL | SINGLE<br>PANEL | DUAL<br>PANEL |           | HR-TFT    |

| K1   | K2    | LCDVD17     |                 |               |                 |               |                 |               |           | LOW       |

| J5   | K1    | LCDVD16     |                 |               |                 |               |                 |               |           | LOW       |

| R10  | T13   | LCDVD15     |                 |               |                 | MLSTN7        |                 | CLSTN7        | Intensity | Intensity |

| P10  | R12   | LCDVD14     |                 |               |                 | MLSTN6        |                 | CLSTN6        | BLUE4     | BLUE4     |

| Т9   | R11   | LCDVD13     |                 |               |                 | MLSTN5        |                 | CLSTN5        | BLUE3     | BLUE3     |

| R9   | T12   | LCDVD12     |                 |               |                 | MLSTN4        |                 | CLSTN4        | BLUE2     | BLUE2     |

| N11  | T11   | LCDVD11     |                 |               |                 | MLSTN3        |                 | CLSTN3        | BLUE1     | BLUE1     |

| K8   | P10   | LCDVD10     |                 |               |                 | MLSTN2        |                 | CLSTN2        | BLUE0     | BLUE0     |

| L11  | K10   | LCDVD9      |                 |               |                 | MLSTN1        |                 | CLSTN1        | GREEN4    | GREEN4    |

| M11  | М9    | LCDVD8      |                 |               |                 | MLSTN0        |                 | CLSTN0        | GREEN3    | GREEN3    |

| M10  | R10   | LCDVD7      |                 | MLSTN3        | MUSTN7          | MUSTN7        | CUSTN7          | CUSTN7        | GREEN2    | GREEN2    |

| M9   | T10   | LCDVD6      |                 | MLSTN2        | MUSTN6          | MUSTN6        | CUSTN6          | CUSTN6        | GREEN1    | GREEN1    |

| N10  | K9    | LCDVD5      |                 | MLSTN1        | MUSTN5          | MUSTN5        | CUSTN5          | CUSTN5        | GREEN0    | GREEN0    |

| L10  | Т9    | LCDVD4      |                 | MLSTN0        | MUSTN4          | MUSTN4        | CUSTN4          | CUSTN4        | RED4      | RED4      |

| N8   | T8    | LCDVD3      | MUSTN3          | MUSTN3        | MUSTN3          | MUSTN3        | CUSTN3          | CUSTN3        | RED3      | RED3      |

| T7   | R8    | LCDVD2      | MUSTN2          | MUSTN2        | MUSTN2          | MUSTN2        | CUSTN2          | CUSTN2        | RED2      | RED2      |

| R7   | P8    | LCDVD1      | MUSTN1          | MUSTN1        | MUSTN1          | MUSTN1        | CUSTN1          | CUSTN1        | RED1      | RED1      |

| P7   | M8    | LCDVD0      | MUSTN0          | MUSTN0        | MUSTN0          | MUSTN0        | CUSTN0          | CUSTN0        | RED0      | RED0      |

- The Intensity bit is identically generated for all three colors.

MU = Monochrome Upper

CU = Color Upper

CL = Color Lower

Table 4. 256-Ball PBGA Package Numerical Pin List

| BGA PIN | SIGNAL            | RESET STATE        | STANDBY STATE                               |

|---------|-------------------|--------------------|---------------------------------------------|

| A1      | TDI               | Input with Pull-up | Input with Pull-up                          |

| A2      | MMCDATA/MMSPIDOUT | Input: MMSPIDOUT   | LOW                                         |

| A3      | MMCCLK/MMSPICLK   | LOW: MMSPICLK      | LOW                                         |

| A4      | ACIN              | Input              | Input                                       |

| A5      | VSS               |                    |                                             |

| A6      | PF0/INT0          | Input: PF0         | No Change                                   |

| A7      | VDDC              |                    |                                             |

| A8      | A27/SCRST         | LOW: A27           | LOW                                         |

| A9      | DQM0              | HIGH               | LOW                                         |

| A10     | SCLK              | LOW                | LOW                                         |

| A11     | VSS               |                    |                                             |

| A12     | nSCS3             | HIGH               | HIGH                                        |

| A13     | A24               | LOW                | LOW                                         |

| A14     | D24               | LOW                | LOW                                         |

| A15     | A23               | LOW                | LOW                                         |

| A16     | D23               | LOW                | LOW                                         |

| B1      | TCK               | Input              | Input                                       |

| B2      | TDO               | Input              | No Change                                   |

| В3      | MMCCMD/MMSPIDIN   | Input: MMSPIDIN    | LOW                                         |

| B4      | ACSYNC            | LOW                | LOW                                         |

| B5      | PF4/INT4/SCVCCEN  | Input: PF4         | LOW if SCI is Enabled; otherwise, No Change |

| В6      | PF1/INT1          | Input: PF1         | No Change                                   |

| B7      | PWM1              | Input              | Input                                       |

| B8      | VDD               |                    |                                             |

| B9      | DQM1              | HIGH               | LOW                                         |

| B10     | CS6/SCKE1_2       | LOW: CS6           | LOW                                         |

| B11     | D30               | LOW                | LOW                                         |

| B12     | D29               | LOW                | LOW                                         |

| B13     | D25               | LOW                | LOW                                         |

| B14     | VDD               |                    |                                             |

| B15     | VSSC              |                    |                                             |

| B16     | A22               | LOW                | LOW                                         |

| C1      | TMS               | Input with Pull-up | Input with Pull-up                          |

| C2      | nEXTPWR           | Input              | Input                                       |

| C3      | MEDCHG            | Input              | Input                                       |

| C4      | ACBITCLK          | Input              | Input                                       |

| C5      | PF7/INT7/PCRDY2   | Input: PF7         | No Change                                   |

| C6      | PF2/INT2          | PF2/INT2           | No Change                                   |

| C7      | PWM0              | Input              | Input                                       |

| C8      | nWE0              | HIGH               | HIGH                                        |

| C9      | VSSC              | 1.000              |                                             |

| C10     | CS7/SCKE0         | LOW: CS7           | LOW                                         |

| C11     | nCAS              | HIGH               | HIGH                                        |

| C12     | nSWE              | HIGH               | HIGH                                        |

| C13     | D26               | LOW                | LOW                                         |

Table 4. 256-Ball PBGA Package Numerical Pin List (Cont'd)

| <b>BGA PIN</b> | SIGNAL            | RESET STATE | STANDBY STATE |

|----------------|-------------------|-------------|---------------|

| C14            | nSCS0             | HIGH        | HIGH          |

| C15            | VSS               |             |               |

| C16            | A21               | LOW         | LOW           |

| D1             | BATOK             | Input       | Input         |

| D2             | nBATCHG           | Input       | Input         |

| D3             | nPOR              | Input       | Input         |

| D4             | WAKEUP            | Input       | Input         |

| D5             | ACOUT             | LOW         | LOW           |

| D6             | PF5/INT5/SCDETECT | Input: PF5  | No Change     |

| D7             | nPWME1            | Input       | Input         |

| D8             | nOE               | HIGH        | HIGH          |

| D9             | DQM2              | HIGH        | LOW           |

| D10            | nWE3              | HIGH        | HIGH          |

| D11            | D31               | LOW         | LOW           |

| D12            | VDDC              |             |               |

| D13            | nSCS1             | HIGH        | HIGH          |

| D14            | D21               | LOW         | LOW           |

| D15            | A20               | LOW         | LOW           |

| D16            | D19               | LOW         | LOW           |

| E1             | VDDC              |             |               |

| E2             | UARTCTS2          | Input       | Input         |

| E3             | UARTDCD2          | Input       | Input         |

| E4             | nPWRFL            | Input       | Input         |

| E5             | UARTDSR2          | Input       | Input         |

| E6             | PF6/INT6/PCRDY1   | Input: PF6  | No Change     |

| E7             | nPWME0            | Input       | Input         |

| E8             | VSS               |             |               |

| E9             | DQM3              | HIGH        | LOW           |

| E10            | VDD               |             |               |

| E11            | nSCS2             | HIGH        | HIGH          |

| E12            | D27               | LOW         | LOW           |

| E13            | A18               | LOW         | LOW           |

| E14            | D18               | LOW         | LOW           |

| E15            | VDDC              |             |               |

| E16            | A17/SB1           | LOW: SBANK1 | LOW           |

| F1             | VDD               |             |               |

| F2             | UARTIRTX1         | LOW         | LOW           |

| F3             | UARTIRRX1         | Input       | Input         |

| F4             | UARTTX2           | HIGH        | HIGH          |

| F5             | COL1              | HIGH        | HIGH          |

| F6             | COL0              | HIGH        | HIGH          |

| F7             | VSS               |             |               |

| F8             | A26/SCCLK         | LOW: A26    | LOW           |

| F9             | nRAS              | HIGH        | HIGH          |

| F10            | D22               | LOW         | LOW           |

Table 4. 256-Ball PBGA Package Numerical Pin List (Cont'd)

| BGA PIN  | SIGNAL                 | RESET STATE       | STANDBY STATE    |

|----------|------------------------|-------------------|------------------|

| F11      | A19                    | LOW               | LOW              |

| F12      | D17                    | LOW               | LOW              |

| F13      | VDD                    |                   |                  |

| F14      | A16/SB0                | LOW: SBANK0       | LOW              |

| F15      | D16                    | LOW               | LOW              |

| F16      | A15/SA13               | LOW: SA13         | LOW              |

| G1       | COL2                   | HIGH              | HIGH             |

| G2       | COL3                   | HIGH              | HIGH             |

| G3       | VSS                    |                   |                  |

| G4       | COL4                   | HIGH              | HIGH             |

| G5       | COL5                   | HIGH              | HIGH             |

| G6       | VSSC                   |                   |                  |

| G7       | VDD                    |                   |                  |

| G8       | A25/SCIO               | LOW: A25          | LOW              |

| G9       | SCKE3                  | LOW               | LOW              |

| G10      | D28                    | LOW               | LOW              |

| G11      | D14                    | LOW               | LOW              |

| G12      | D15                    | LOW               | LOW              |

| G13      | A14/SA12               | LOW: SA12         | LOW              |

| G14      | A13/SA11               | LOW: SA11         | LOW              |

| G15      | D13                    | LOW               | LOW              |

| G16      | A12/SA10               | LOW: SA10         | LOW              |

| H1       | COL6                   | HIGH              | HIGH             |

| H2       | COL7                   | HIGH              | HIGH             |

| H3       | TBUZ                   | LOW               | LOW              |

| H4       | SSPCLK                 | LOW               | LOW              |

| H5       | VSSC                   |                   |                  |

| H6       | nURESET                | Input             | Input            |

| H7       | VSS                    |                   |                  |

| H8       | PF3/INT3               | Input: PF3        | No Change        |

| H9       | VSS                    | 1.004             | Low              |

| H10      | D20                    | LOW               | LOW              |

| H11      | D6                     | LOW               | LOW              |

| H12      | VSSC                   | 1.014             | LOW              |

| H13      | D12                    | LOW               | LOW              |

| H14      | A11/SA9                | LOW: SA9          | LOW              |

| H15      | D11                    | LOW               | LOW              |

| H16      | A10/SA8                | LOW: SA8          | LOW              |

| J1       | SSPRX                  | Input             | Input            |

| J2       | SSPTX<br>SSPERM/SSPERM | LOW               | LOW              |

| J3       | SSPFRM/nSSPFRM<br>VDDC | Input: nSSPFRM    | Input            |

| J4<br>J5 | PA0/LCDVD16            | Input: DAC        | No Chango        |

| J6       | PGMCLK                 | Input: PA0<br>LOW | No Change<br>LOW |

| J6<br>J7 | UARTRX2                |                   |                  |

| J/       | UARTRAZ                | Input             | Input            |

Table 4. 256-Ball PBGA Package Numerical Pin List (Cont'd)