Rev. V3

#### **Features**

- 4 Bit Digital Phase Shifter

- 360° Coverage with LSB = 22.5°

- Integrated CMOS Driver

- Serial or Parallel Control

- Low DC Power Consumption

- Minimal Attenuation Variation over Phase Shift Range

- 50 Ω Impedance

- EAR99

- Lead-Free 4 mm 24-Lead PQFN Package

- RoHS\* Compliant

## **Description**

The MAPS-010145 is a GaAs pHEMT 4-bit digital phase shifter with an integrated CMOS driver in a 4 mm PQFN plastic surface mount package. Step size is 22.5° providing phase shift from 0° to 360° in 22.5° steps. This design has been optimized to minimize variation in attenuation over the phase shift range.

The MAPS-010145 is ideally suited for use where high phase accuracy with minimum loss variation over the phase shift range are required. The 4 mm PQFN package provides a smaller footprint than is typically available for a digital phase shifter with an internal driver. Typical applications include communications antennas and phased array radars.

## Ordering Information<sup>1</sup>

| Part Number        | Package           |

|--------------------|-------------------|

| MAPS-010145-TR0500 | 500 piece reel    |

| MAPS-010145-001SMB | Sample Test Board |

1. Reference Application Note M513 for reel size information.

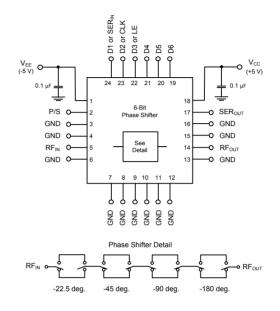

#### **Functional Schematic**

## Pin Configuration<sup>2</sup>

| Pin No. | Function         | Pin No. | Function                |

|---------|------------------|---------|-------------------------|

| 1       | V <sub>EE</sub>  | 13      | GND                     |

| 2       | P/S              | 14      | RF <sub>OUT</sub>       |

| 3       | GND              | 15      | GND                     |

| 4       | GND              | 16      | GND                     |

| 5       | RF <sub>IN</sub> | 17      | SER <sub>OUT</sub>      |

| 6       | GND              | 18      | V <sub>CC</sub>         |

| 7       | GND              | 19      | D6                      |

| 8       | GND              | 20      | D5                      |

| 9       | GND              | 21      | D4                      |

| 10      | GND              | 22      | D3 or LE                |

| 11      | GND              | 23      | D2 or CLK               |

| 12      | GND              | 24      | D1 or SER <sub>IN</sub> |

2. The exposed pad centered on the package bottom must be connected to RF, DC and thermal ground.

1

<sup>\*</sup> Restrictions on Hazardous Substances, European Union Directive 2011/65/EU.

# MAPS-010145

Digital Phase Shifter 4-Bit, 3.5 - 6.0 GHz

Rev. V3

## **Electrical Specifications:**

Freq. = 3.5 - 6.0 GHz,  $T_A$  = 25°C,  $Z_0$  = 50  $\Omega$ ,  $V_{CC}$  = +5.0 V,  $V_{EE}$  = -5.0 V

| Parameter                                                       | Test Conditions                                                                   | Units | Min.                         | Тур.                                      | Max.                  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------------------------------|-------------------------------------------|-----------------------|

| Operating Power <sup>3</sup>                                    | 3.5 - 6.0 GHz                                                                     | dBm   | _                            | _                                         | +25                   |

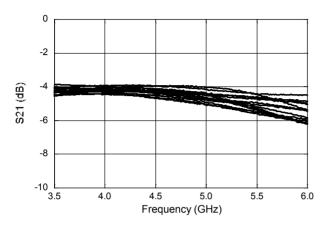

| Insertion Loss<br>(Any Phase State)                             | Any Phase State                                                                   | dB    | _                            | 5.0                                       | 6.5                   |

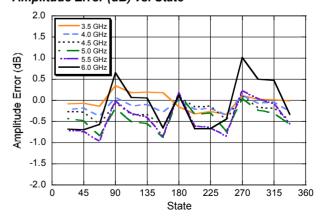

| Attenuation Variation                                           | Across All Phase States                                                           | dB    | _                            | ± 1                                       | _                     |

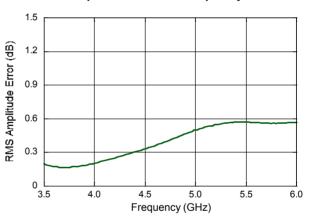

| RMS Attenuation Error 4                                         | All Values Relative to Insertion Loss at Reference Phase                          | dB    | _                            | 0.4                                       | _                     |

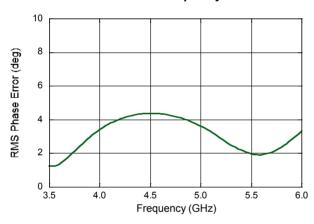

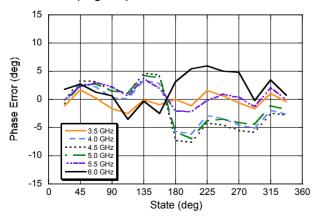

| RMS Phase Error <sup>4</sup>                                    | All Values Relative to Reference Phase                                            | deg   | _                            | 3                                         | _                     |

| Phase Accuracy <sup>5</sup><br>Relative to Reference Loss State | 22.5 Degree Bit 45 Degree Bit 90 Degree Bit 180 Degree Bit Sum of All Bits        | deg   | _                            | ± 1.7<br>± 1.0<br>± 2.0<br>± 3.5<br>± 2.5 | _                     |

| VSWR                                                            | RF Input<br>RF Output                                                             | Ratio | _                            | 1.8:1<br>1.8:1                            | _                     |

| 1 dB Compression                                                | Reference State                                                                   | dBm   | _                            | 27                                        | _                     |

| Input IP3                                                       | Two-tone inputs up to +5 dBm                                                      | dBm   | _                            | 45                                        | _                     |

| T <sub>RISE</sub> , T <sub>FALL</sub>                           | 10% to 90% RF, 90% to 10% RF                                                      | ns    | _                            | 50                                        | _                     |

| V <sub>CC</sub><br>V <sub>EE</sub>                              | <del>-</del>                                                                      | V     | 3.0<br>-5.5                  | <u> </u>                                  | 5.5<br>-3.0           |

| V <sub>IL</sub><br>V <sub>IH</sub>                              | LOW-level input voltage<br>HIGH-level input voltage                               | V     | 0.0<br>0.7 x V <sub>CC</sub> | _                                         | 0.3 x V <sub>CC</sub> |

| I <sub>IN</sub> (Input Control Current)                         | $V_{IN} = V_{CC}$ or GND                                                          | μA    | _                            | 1                                         | _                     |

| V <sub>OH</sub><br>V <sub>OL</sub>                              | For serial out; $I_{OH}$ = -100 $\mu$ A<br>For serial out; $I_{OL}$ = 100 $\mu$ A | V     | V <sub>CC</sub> - 0.2        | _                                         | 0.2                   |

| I <sub>CC</sub><br>(Quiescent Supply Current)                   | $V_{CONTROL} = V_{CC}$ or GND                                                     | μA    | _                            | _                                         | 2                     |

| I <sub>EE</sub>                                                 | $V_{EE}$ min to max $V_{IN} = V_{IL}$ or $V_{IH}$                                 | mA    | -1.0                         | -0.1                                      | _                     |

<sup>3.</sup> Maximum operating power is the maximum power where the specifications are guaranteed.

<sup>4.</sup> RMS is calculated across all 15 amplitude or phase states relative to the amplitude or phase in the 0° phase state at a given frequency.

<sup>5.</sup> This phase shifter is guaranteed to have monotonic phase shift.

Rev. V3

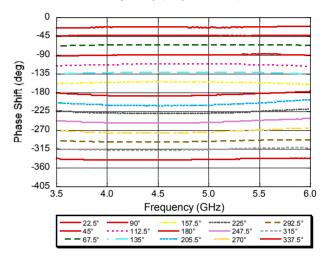

## **Typical Performance Curves**

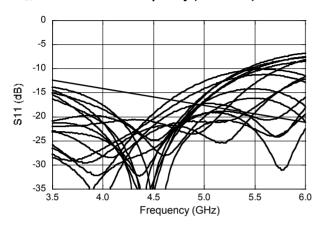

#### RFIN Return Loss vs. Frequency (All States)

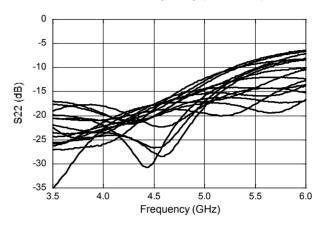

#### RF<sub>OUT</sub> Return Loss vs. Frequency (All States)

#### Mean RMS Phase Error vs. Frequency

#### Mean RMS Amplitude Error vs. Frequency

#### Phase Error (degrees) vs. State

#### Amplitude Error (dB) vs. State

Rev. V3

## **Typical Performance Curves**

#### Amplitude Variation vs. Phase State

#### Phase Shift vs. Frequency (Major States)

## Absolute Maximum Ratings<sup>6,7</sup>

| Parameter                        | Absolute Maximum                                                                    |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| Input Power<br>3.5 - 6.0 GHz     | +27 dBm                                                                             |  |  |  |

| V <sub>CC</sub>                  | -0.5 V ≤ V <sub>CC</sub> ≤ +7.0 V                                                   |  |  |  |

| V <sub>EE</sub>                  | -7.0 V ≤ V <sub>EE</sub> ≤ +0.5 V                                                   |  |  |  |

| D1-D4, P/S, LE, CLK or<br>SER IN | $-0.5 \text{ V} \le \text{V}_{\text{IN}} \le \text{V}_{\text{CC}} + 0.5 \text{ V}$  |  |  |  |

| SER OUT                          | $-0.5 \text{ V} \le \text{V}_{\text{OUT}} \le \text{V}_{\text{CC}} + 0.5 \text{ V}$ |  |  |  |

| Operating Temperature            | -40°C to +85°C                                                                      |  |  |  |

| Storage Temperature              | -65°C to +150°C                                                                     |  |  |  |

<sup>6.</sup> Exceeding any one or combination of these limits may cause permanent damage to this device.

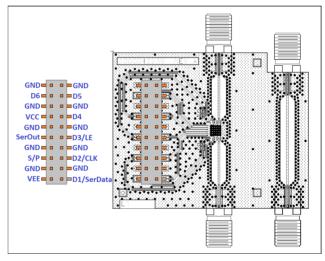

## Sample Board Header Pin Labels

## **Handling Procedures**

Please observe the following precautions to avoid damage:

## **Static Sensitivity**

Gallium Arsenide and Silicon Integrated Circuits are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these devices.

4

MACOM does not recommend sustained operation near these survivability limits.

Rev. V3

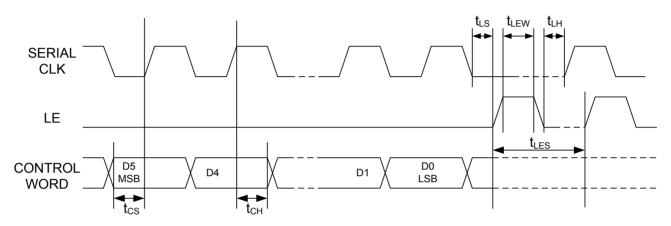

#### Modes of Operation: Serial and Direct Parallel

#### Serial Mode

The serial control interface (SERIN, CLK, LE, SEROUT) is compatible with the SPI protocol. SPI mode is activated when P/S is kept high. The 6-bit serial word must be loaded with the MSB first. After shifting in the 6 bit word, a rising edge on LE will set the phase shifter to the desired state. While LE is high the CLK is masked to protect the data while implementing the change. SEROUT is SERIN delayed by 6 clock cycles.

When P/S is low, the serial control interface is disabled. When P/S is set high, Pins 22, 23, and 24 have the LE, CLK, and SER IN function.

In serial mode operation, the outputs will stay constant while LE is kept low.

#### Direct Parallel Mode

The parallel mode is enabled when P/S is set low. In the direct parallel mode, the phase shifter is controlled by the parallel control inputs directly. When P/S is set low, Pins 22, 23, and 24 have the D3, D2, and D1 function.

## Mode Truth Table<sup>8,9</sup>

| P/S | LE  | Mode            |

|-----|-----|-----------------|

| 1   | Х   | Serial          |

| 0   | N/A | Direct Parallel |

- 8. There are two dummy bits (D1 & D2), that must be sent in the serial mode. This is because the 4 bit phase shifter uses the same driver as the 6 bit phase shifter.

- 9. In the parallel mode, D1 and D2 should be tied to ground or to  $V_{\text{CC}}$ .

## Truth Table (Digital Phase Shifter)<sup>10</sup>

| D6 | D5 | D4 | D3 | D2 | D1 | Phase Shift     |

|----|----|----|----|----|----|-----------------|

| 0  | 0  | 0  | 0  | Х  | Х  | Reference Phase |

| 0  | 0  | 0  | 1  | Х  | Х  | 22.5°           |

| 0  | 0  | 1  | 0  | Х  | Χ  | 45°             |

| 0  | 1  | 0  | 0  | Х  | Х  | 90°             |

| 1  | 0  | 0  | 0  | Х  | Х  | 180°            |

| 1  | 1  | 1  | 1  | Х  | Х  | 337.5°          |

10. 0 = CMOS Low; 1 = CMOS High, X is CMOS Low or High

#### **Serial Interface Timing Characteristics**

| Symbol           | Parameter                           | Ту    |      |       |       |

|------------------|-------------------------------------|-------|------|-------|-------|

|                  |                                     | -40°C | 25°C | +85°C | Units |

| t <sub>sck</sub> | Min. Serial Clock Period            | 100   | 100  | 100   | ns    |

| t <sub>cs</sub>  | Min. Control Set-up Time            | 20    | 20   | 20    | ns    |

| t <sub>сн</sub>  | Min. Control Hold Time              | 20    | 20   | 20    | ns    |

| t <sub>LS</sub>  | Min. LE Set-up Time                 | 10    | 10   | 10    | ns    |

| t <sub>LEW</sub> | Min. LE Pulse Width                 | 10    | 10   | 10    | ns    |

| t <sub>LH</sub>  | Min. Serial Clock Hold Time from LE | 10    | 10   | 10    | ns    |

| t <sub>LES</sub> | Min. LE Pulse Spacing               | 630   | 630  | 630   | ns    |

Rev. V3

# Functionality Modes of Operation: Serial and Direct Parallel

#### **Serial Input Interface Timing Diagram**

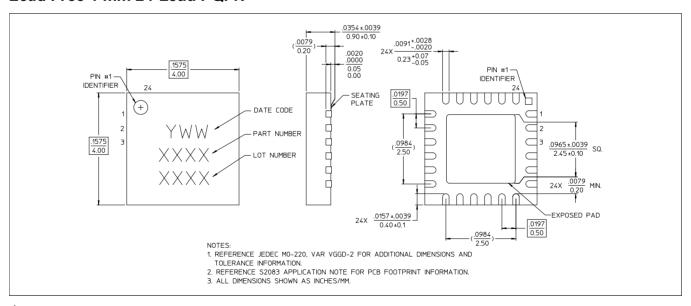

#### Lead Free 4 mm 24-Lead PQFN †

<sup>&</sup>lt;sup>†</sup> Reference Application Note S2083 for lead-free solder reflow recommendations. Meets JEDEC moisture sensitivity level 1 requirements. Plating is 100% matte tin over copper.

## MAPS-010145

Digital Phase Shifter 4-Bit, 3.5 - 6.0 GHz

Rev. V3

#### MACOM Technology Solutions Inc. All rights reserved.

Information in this document is provided in connection with MACOM Technology Solutions Inc ("MACOM") products. These materials are provided by MACOM as a service to its customers and may be used for informational purposes only. Except as provided in MACOM's Terms and Conditions of Sale for such products or in any separate agreement related to this document, MACOM assumes no liability whatsoever. MACOM assumes no responsibility for errors or omissions in these materials. MACOM may make changes to specifications and product descriptions at any time, without notice. MACOM makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppels or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MACOM PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MACOM FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MACOM SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

MACOM products are not intended for use in medical, lifesaving or life sustaining applications. MACOM customers using or selling MACOM products for use in such applications do so at their own risk and agree to fully indemnify MACOM for any damages resulting from such improper use or sale.