16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

- Fully Integrated

- 1200V Blocking Voltage

- No External Components

- Fast Turn-Off Time

- CMOS Compatible Input

- · Low Rds On

- Small TO263HV Package

- Low Energy Loss 140uW/A

- For Frequencies < 10kHz

### **Description**

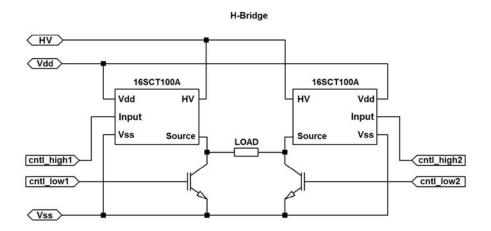

The 16SCT100 is a 1200V 15A fully integrated high-side switch typically used in systems requiring H-bridges. The chip's integrated circuitry drives an integrated MOSFET gate above the HV supply to ensure that the transistor is adequately saturated. All control lines are low voltage. Package creepage distances allow for 1200V operation without the use of conformal coating or slots.

### **Typical applications**

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

### **Absolute maximum ratings**

| HV Power Supply (HV - Vss)      | 1200 V        |

|---------------------------------|---------------|

| HV to Source Voltage (HV - Vs)  | 1200 V        |

| Negative Source Voltage         | 500 V         |

| Continuous Source Current (25C) | 15A           |

| Pulse Source Current (25C)      | 19A           |

| Vdd Power Supply (Vdd - Vss)    | 18V           |

| Operating Junction temperature  | -40 C to 150C |

| Storage temperature             | -65 C to 150C |

### **Recommended Maximum Operating Conditions**

| PARAMETER                       | MIN | MAX  | UNIT |

|---------------------------------|-----|------|------|

| Operating voltage (HV - Vss)    | 40  | 1000 | V    |

| Operating voltage (HV - Source) | 0   | 1000 | V    |

| Operating voltage (Vdd - Vss)   | 6   | 18   | V    |

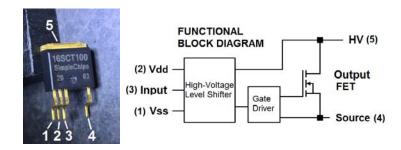

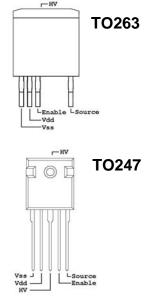

#### Pin-out

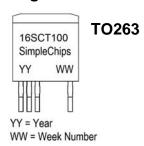

### Marking

**TO247**

#### **Pin Definitions**

| Pin# | SYMBOL | DESCRIPTION               |

|------|--------|---------------------------|

| 1    | Vss    | Ground                    |

| 2    | Vdd    | Low Voltage Supply        |

| 3    | Input  | Input signal (CMOS logic) |

| 4    | Source | Output fet source         |

| 5    | HV     | High Voltage Supply       |

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

#### **Thermal Information**

|   | SYMBOL             | Thermal Metric                                                                           |    | Unit |

|---|--------------------|------------------------------------------------------------------------------------------|----|------|

| 1 | R <sub>⊕JA05</sub> | Junction-to-ambient thermal resistance double sided 0.5in2 top-copper                    | 50 | C/W  |

| 2 | R <sub>⊕JA25</sub> | Junction-to-ambient thermal resistance double sided 2.5in2 top-copper                    |    | C/W  |

| 3 | R <sub>⊕JA30</sub> | Junction-to-ambient thermal resistance double sided 3in2 top-copper +16in2 bottom copper | 20 | C/W  |

| 4 | $R_{\Theta JC}$    | Junction to Case (top) thermal resistance                                                | 2  | C/W  |

### Static Electrical Characteristics ( $25^{\circ}\text{C} \pm 5^{\circ}\text{C}$ unless specified)

| SYMBOL             | PARAMETER                    | TEST CONDITIONS              | MIN  | TYP  | MAX  | UNIT |

|--------------------|------------------------------|------------------------------|------|------|------|------|

| I <sub>HVoff</sub> | HV off-state current         | Vdd = 18V HV = 1000V         |      |      | 260  | μΑ   |

| I <sub>HVon</sub>  | HV on-state current          | Vdd = 18V HV = 100V          |      |      | 5.0  | mA   |

| I <sub>Vdd</sub>   | Vdd off state current        | Vdd = 18V HV = 1200V         | -100 |      | 100  | nA   |

| IE                 | Input current                | V <sub>E</sub> = 18V         | 0    | 0.01 | 1.0  | μΑ   |

| V <sub>DS</sub>    | HV to Source voltage at 5.3A | V <sub>HV</sub> = 600V       | 0    | 1.10 | 1.40 | V    |

| R <sub>DS</sub>    | Saturation resistance at 1A  | V <sub>HV</sub> = 600V; I=1A | 0    | 210  | 260  | mΩ   |

# Dynamic Electrical Characteristics (R<sub>load</sub>: 150 $\Omega$ , 25°C ± 5°C)

| SYMBOL            | PARAMETER                                 | TEST CONDITIONS      | MIN  | TYP  | MAX  | UNIT |

|-------------------|-------------------------------------------|----------------------|------|------|------|------|

| Idd6V             | On-state Vdd current                      | HV = 100V, Vdd = 6V  | 0.27 | 0.40 | 0.70 | mA   |

| ldd12V            | On-state Vdd current                      | HV = 100V, Vdd = 12V | 0.70 | 1.30 | 2.50 | mA   |

| ldd18V            | On-state Vdd current                      | HV = 100V, Vdd = 18V | 2.00 | 3.00 | 5.00 | mA   |

| Ihv6V             | On-state HV current                       | HV = 800V, Vdd = 6V  | 2.0  | 2.6  | 4.0  | mA   |

| lhv12V            | On-state HV current                       | HV = 800V, Vdd = 12V | 4.0  | 5.7  | 8.0  | mA   |

| lhv18V            | On-state HV current                       | HV = 800V, Vdd = 18V | 4.5  | 6.2  | 9.0  | mA   |

| t <sub>dr6</sub>  | Load Current Rise Time Delay to 10%       | HV = 800V, Vdd = 6V  | 0.30 | 0.69 | 1.20 | μS   |

| t <sub>r6</sub>   | Load Current Rise Time 10%-90%            | HV = 800V, Vdd = 6V  | 0.25 | 0.56 | 1.20 | μS   |

| t <sub>df6</sub>  | Load Current Fall Time Delay to 90%       | HV = 800V, Vdd = 6V  | 0.80 | 1.70 | 2.50 | μS   |

| t <sub>f6</sub>   | Load Current Fall Time 90%-10%            | HV = 800V, Vdd = 6V  | 0.03 | 0.07 | 0.50 | μS   |

| t <sub>dr12</sub> | Load Current Rise Time Delay to 10%       | HV = 800V, Vdd = 12V | 0.20 | 0.43 | 1.00 | μS   |

| t <sub>r12</sub>  | Load Current Rise Time 10%-90%            | HV = 800V, Vdd = 12V | 0.20 | 0.50 | 1.00 | μS   |

| t <sub>df12</sub> | Load Current Fall Time Delay to 90%       | HV = 800V, Vdd = 12V | 0.60 | 1.05 | 2.00 | μS   |

| t <sub>f12</sub>  | Load Current Fall Time 90%-10%            | HV = 800V, Vdd = 12V | 0.03 | 0.08 | 0.50 | μS   |

| t <sub>dr18</sub> | Load Current Rise Time Delay to 10%       | HV = 800V, Vdd = 18V | 0.15 | 0.34 | 0.80 | μS   |

| t <sub>r18</sub>  | Load Current Rise Time 10%-90%            | HV = 800V, Vdd = 18V | 0.20 | 0.44 | 0.90 | μS   |

| t <sub>df18</sub> | Load Current Fall Time Delay to 90%       | HV = 800V, Vdd = 18V | 0.50 | 0.89 | 1.70 | μS   |

| t <sub>f18</sub>  | Load Current Fall Time 90%-10%            | HV = 800V, Vdd = 18V | 0.03 | 0.07 | 0.50 | μS   |

| t <sub>c</sub>    | Minimum Time between Turn-Off and Turn-On | HV = 40V, Vdd = 6V   | 20.0 |      |      | μS   |

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

## Output Fet Reverse Diode Characteristics ( $25^{\circ}C \pm 5^{\circ}C$ )

| SYMBOL              | PARAMETER                  | TEST CONDITIONS                                                              | MIN | TYP | MAX | UNIT |

|---------------------|----------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>r</sub>      | Continuous Reverse Current |                                                                              |     |     | 19  | A    |

| V <sub>SHV</sub>    | LoadDiode Forward Voltage  | E = 0V, Vdd = 8V,<br>HV = 0V, I <sub>r</sub> = 5A                            |     | 3.3 |     | V    |

| t <sub>rr</sub>     | Reverse Recovery Time      | $E = 0V$ , $Vdd = 8V$ , $dI_f/dt = 3000A/\mu s$<br>$HV = 800V$ , $I_r = 10A$ | 20  |     |     | nS   |

| t <sub>flLoad</sub> | Reverse Recovery Charge    | $E = 0V$ , $Vdd = 8V$ , $dI_f/dt = 3000A/\mu s$<br>$HV = 800V$ , $I_r = 10A$ | 100 |     |     | nC   |

| I <sub>rr</sub> Max | Maximum Recovery Current   | $E = 0V$ , $Vdd = 8V$ , $dI_f/dt = 3000A/\mu s$<br>$HV = 800V$ , $I_r = 10A$ | 8.5 |     |     | Α    |

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

### **Typical Electrical Characteristics**

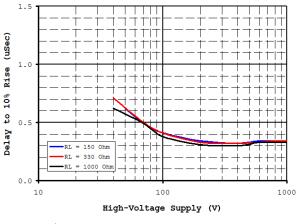

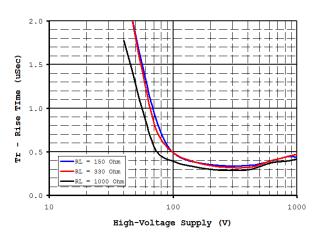

Figure 1: Rise Time Delay for different Resistive Loads at Vdd = 18V

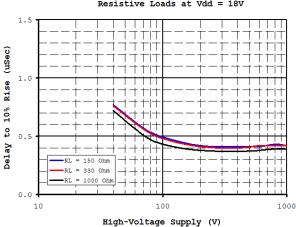

Figure 2: Rise Time Delay for different Resistive Loads at Vdd = 12V

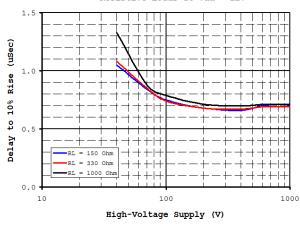

Figure 3: Rise Time Delay for different Resistive Loads at Vdd = 6V

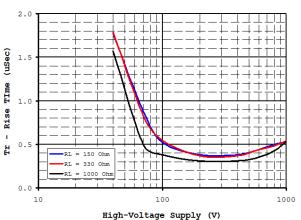

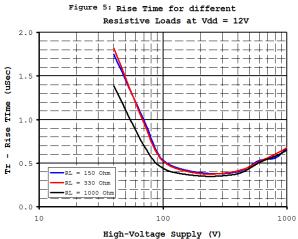

Figure 4: Rise Time for different

Resistive Loads at Vdd = 18V

magn versuge suppart (v)

Figure 6: Rise Time for different

Resistive Loads at Vdd = 6V

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

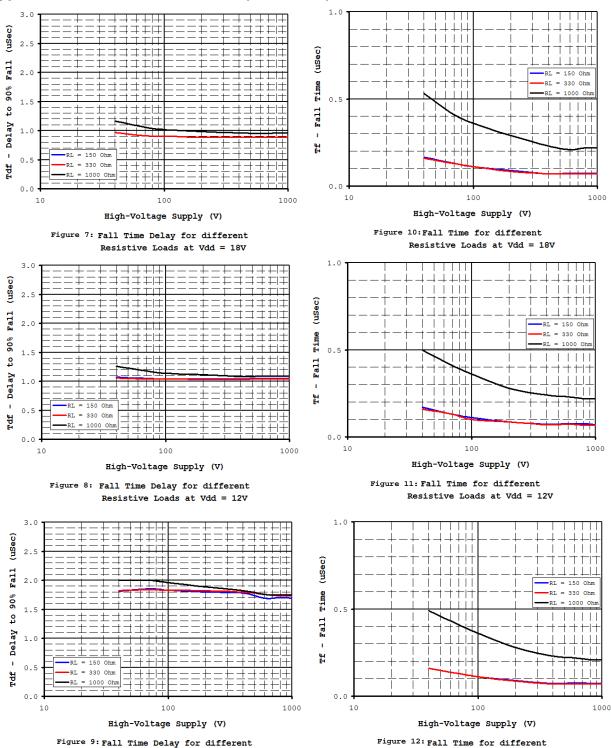

### **Typical Electrical Characteristics (continued)**

Figure 9: Fall Time Delay for different Resistive Loads at Vdd = 6V

Resistive Loads at Vdd = 6V

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

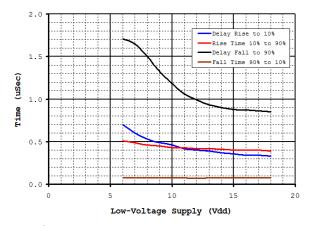

### **Typical Electrical Characteristics (continued)**

Figure 13: Timing for different Vdd at RL=330 $\Omega$

Figure 14: Fall Time for different pulse width  $Vdd{=}12V, \ HV{=}600V \ \text{at RL}{=}330\Omega$

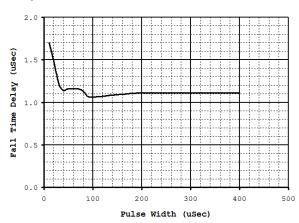

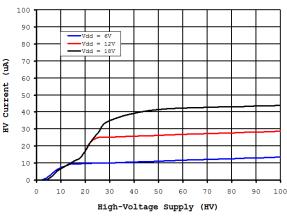

Figure 15: High-Voltage Off-Current for different Vdd

Figure 16: High-Voltage Off-Current for different Vdd

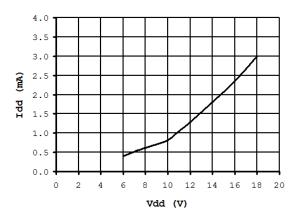

Figure 17: Vdd "On" Current as a function of Vdd  $\,$

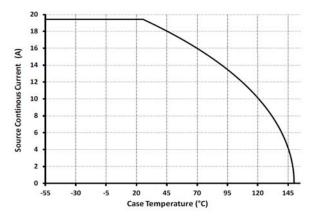

Figure 18: Source maximum current as a function of case temperature.

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

### **Typical Electrical Characteristics (continued)**

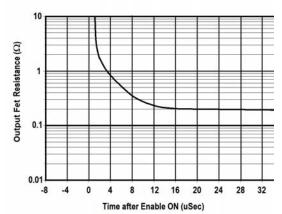

Figure 19: Settling of the output fet resistance after turn on.

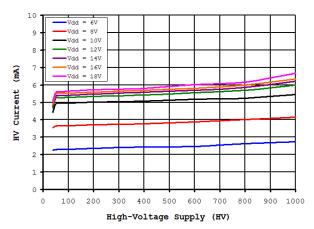

Figure 29: High-Voltage On-Current for different Vdd

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

### **Typical Electrical Characteristics (continued)**

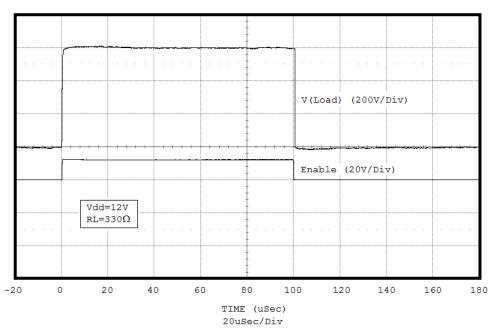

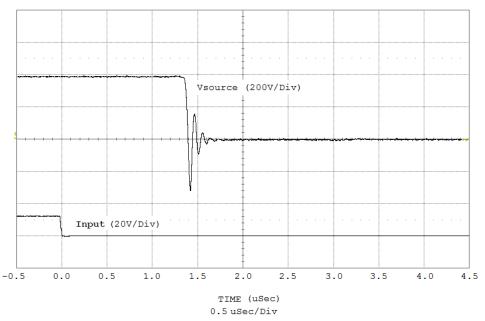

Figure 20: Typical waveform for 600V/100uSec pulse into a 3300hm load resistor

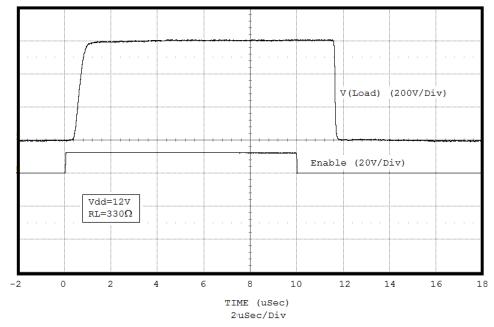

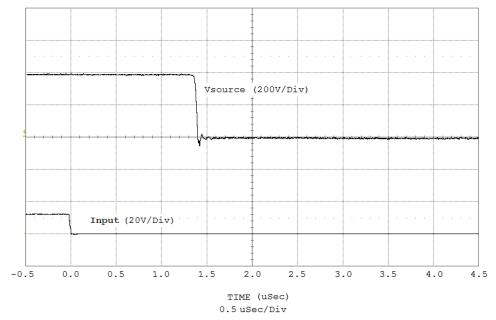

Figure 21: Typical waveform for 600V/10uSec pulse into a 330 Ohm load resistor

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

#### **Relevent Electrical Characteristics**

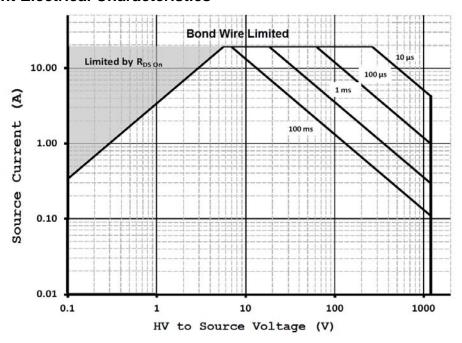

Figure 22: Safe Operating Area for Source Current

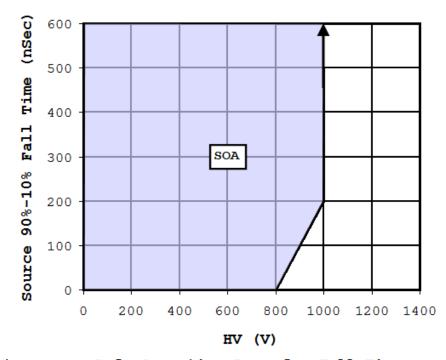

Figure 23: Safe Operating Area for Fall Time

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

### **Relevent Electrical Characteristics (Cont.)**

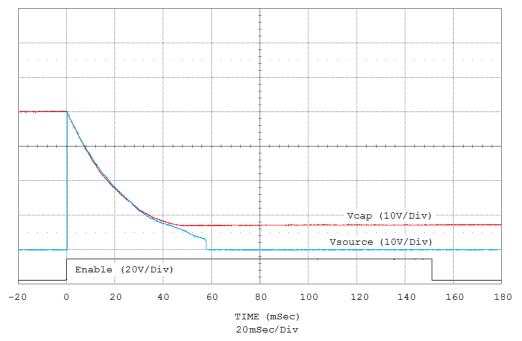

Figure 24: 16SCT100 driving an inductive 470hm resistor at 400V showing negative Source voltage of about -300V after cut-off.

Figure 26:16SCT100 driving an inductive 470hm resistor and an anti-parallel SiC diode at 400V.

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

### **Relevent Electrical Characteristics (Cont.)**

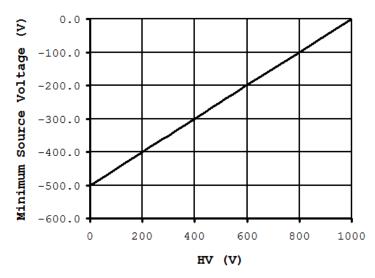

Figure 25: Maximum Permissible Negative Transient

Source Voltage as a function of HV.

(Exceeding these values may permanently damage the 16SCT100)

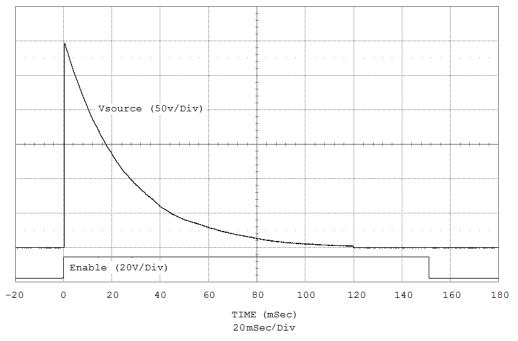

Figure 27: Typical waveform for discharging a 190uF capacitor with 300V into a  $150\Omega$  resistor using the 16SCT100.

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

### **Relevent Electrical Characteristics (Cont.)**

Figure 27: Typical waveform for discharging a 190uF capacitor with 300V into a  $150\Omega$  resistor using the 16SCT100.

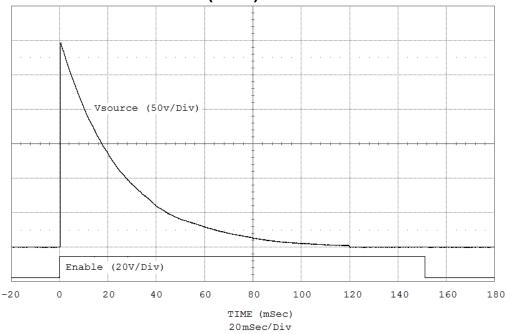

Figure 28: Typical waveform for discharging a 190uF capacitor with 40V into a  $150\Omega$  resistor using the 16SCT100.

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

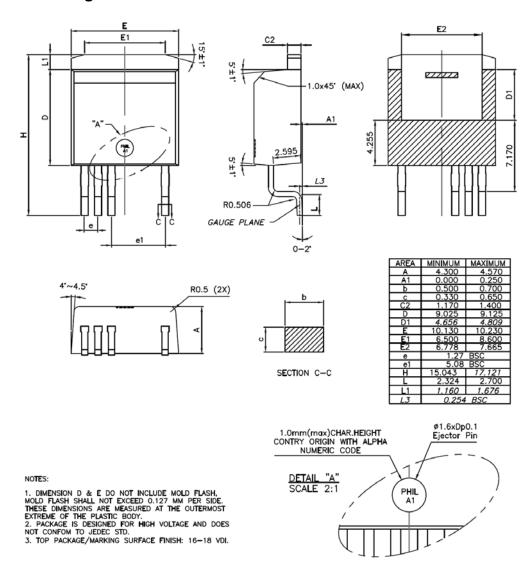

### **TO-263HV Package Mechanical Information**

## **TO-263HV Package Thermal Characteristics**

| PARAMETER              | TEST CONDITIONS                  | TYP | UNIT |

|------------------------|----------------------------------|-----|------|

| Thermal Resistance 0.9 | Copper area = 0.9cm <sup>2</sup> | 56  | C/W  |

| Thermal Resistance 3.2 | Copper area = 3.2cm <sup>2</sup> | 35  | C/W  |

| Thermal Resistance 6.4 | Copper area = 6.4cm <sup>2</sup> | 26  | C/W  |

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

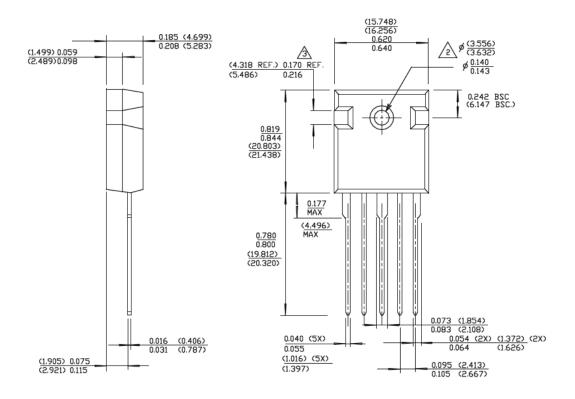

### **TO-247-5 Package Mechanical Information**

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

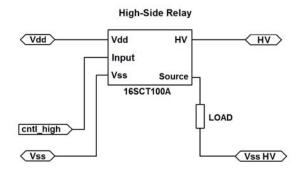

### **Application notes**

The 16SCT100 package (TO-263HV) is a very effective solution for compact systems where saving space is a premium. Requiring no external component in most cases, its implementation is very straight forward. Like every integrated solution there are a few characteristics worth exploring in typical applications.

#### **Minimum Operating Voltage:**

This datasheet states the minimum operating voltage as 40V. This specification actually sells short the capability of the 16SCT100. 40V is the minimum voltage where starting a pulse is guaranteed. However once this pulse is started, the "on" condition will be retained down to voltages below 10V.

For example Figure 27 shows the 16SCT100 source voltage during the discharge of a 190uF capacitor charged with 300V through a 150 Ohm resistor on the source of the 16SCT100. We can see that the source voltage (current through the resistor) keeps flowing down to below 10V. It stops at about 120mSec on this chart.

Figure 28 shows more details of this behaviour on a pulse which is started with 40V on the same capacitor (red curve). We can clearly see that the capacitor discharges nicely down to below 10V (about 7V) before the 16SCT100 cannot keep the current flowing.

#### **Dealing with inductive Loads:**

The 16SCT100 was designed to drive resistive and inductive loads and some of its characteristics make it particularly interesting for driving inductive loads. In doing so the user needs to be careful about a few things.

If a negative voltage excursion is present on the source it should not go below the values shown in Figure 25. Doing so may irreversibly damage the chip. This being said the range of acceptable negative voltage excursion (several hundred volts) is substantial.

This negative excursion allowance make the 16SCT100 specially useful in driving inductive loads in discontinuous mode where the ringing following the load cut-off can be paticularly challenging to manage. The user has simply to ensure that under worse -case scenario the ringing will not exceed the values in figure 25 and the system can be left to naturally settle if desired.

With HV at 400V driving an inductive resistor (see Figure 24) the negative source voltage excursion reaches about -300V. The 16SCT100 will tolerate this without damage, meaning that an anti-parallel diode (as used in Figure 26) in not necessary. Therefore this robustness to negative voltages make the 16SCT100 useful in driving inductive loads without additional anti-parallel diodes, provided the resulting ringing does not affect other parts of the circuit.

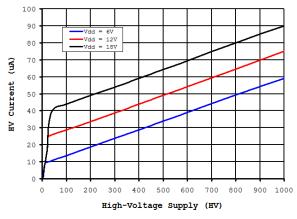

#### Fast fall times at high voltages:

The output FET of the 16SCT100 has a very fast fall time typically less than 100nSec for voltage drops of several hundred volts. This gives dV/dt of the order of 10,000V/uSec. Obviously this can impact neighboring parts of the circuit but also the chip itself.

To control this we have defined a Safe Operating Area (SOA) as per Figure 23 where below 800V any fall time is acceptable while at 1000V the fall time should be at least 200nSec. Violating these SOA limits may permanently damage the 16SCT100.

16SCT100 - PRELIMINARY SPECIFICATION - REVISION OCTOBER 14, 2020

To reduce the fall dV/dt the user can simply add a small capacitance in parallel with the load. Usually a few nF are sufficient to bring the dV/dt to a few 1000V/uSec. Since the 16SCT100 rise time is of this order of magnitude (about 0.4uSec) the application should be insensitive to this.

#### **High Source Current Operation:**

The 16SCT100 will allow driving loads at up to 19A provided the junction temperature does not exceed 150C. Care should be taken to properly manage transient thermal conditions (Figure 22) and/or to properly heat sink the device while maintaining high-voltage isolation.

#### TO-263HV package (see Package Mechanical Information):

This package allows up to 1200V isolation without using conformal coating and/or slots to meet UL 60950 (1200V clearance >= 3.9mm; creepage >= 3.9mm). The package offers pad-pin clearance of 7.17mm and creepage of 6.85mm, well in excess of the 3.9mm. The separation between the source pin and the input pin is 4.38mm minimum (e1 - b(max)), also well in excess of the 3.9mm requirement at 1200V.

#### Maximum operating frequency:

The 16SCT100 has modest delays and rise time but has a fast fall time. This circuit is best suited for operation at fequencies below 10kHz. With delays to rise of about 500nSec and about the same for rise time it is very fast compared to an optically coupled high-side switch (mSec!) but about an order of magnitude slower than a typical low voltage high-side driver (~20-50nSec). The longest timing is the delay to fall time at about 1uSec. So this circuit turns on at 90% in about 1uSec and turns off to 10% in also about 1uS at Vdd=12V. This circuit is very well suited for acting as a high-side switch or high-side relay and can be used also in H-bridge configurations where the switching frequencies are below 10kHz.