#### **General Description**

The MAX7447 4-channel, buffered video reconstruction filter is ideal for anti-aliasing and DAC-smoothing video applications or wherever analog video is reconstructed from a digital data stream (such as cable/satellite/terrestrial set-top boxes, DVD players, hard disk recorders (HDRs), and personal video recorders (PVRs)). This device operates from a single +5V supply and has a flat passband out to 5MHz with a stopband attenuation of 43dB at 27MHz. This makes it ideal for use with NTSC, PAL, and standard-definition digital TV (SDTV) video systems. Each output is capable of driving two standard  $150\Omega$  video loads.

The MAX7447 processes S-Video and CVBS video signals. The video output buffers have a fixed gain of +6dB. Each channel has high-frequency boost circuitry that provides picture sharpness with up to +1.2dB of gain boost without degradation in the stopband. The output video drivers can be disabled with an external pin.

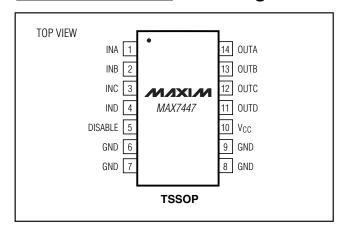

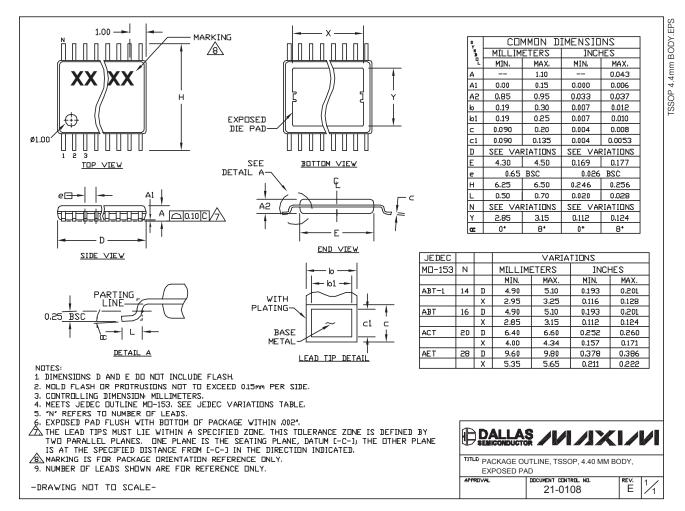

The MAX7447 is available in a 14-pin TSSOP package with an exposed pad, and is specified over the -40°C to +85°C extended temperature range.

#### **Applications**

Set-Top Boxes/HDRs Game Consoles Desktop Video Editors **DVD Players** Digital VCRs

# **Features**

- ♦ 4-Channel Filter and Buffer for S-Video and **CVBS Signals**

- ♦ Filter Response Ideal for NTSC, PAL, and Interlaced SDTV Video Signals

- ◆ 43dB (typ) Stopband Attenuation at 27MHz

- ♦ ±0.75dB (max) Passband Ripple Out to 5MHz

- ♦ Blanking Level Voltage on Output <1V</p>

- ♦ Each Channel Drives Two 150Ω Video Loads

- ♦ +5V Single-Supply Voltage

- ♦ Small 14-Pin TSSOP Package

### **Ordering Information**

| PART       | TEMP PIN-<br>RANGE PACKAGE |              | PACKAGE<br>CODE |  |

|------------|----------------------------|--------------|-----------------|--|

| MAX7447EUD | -40°C to<br>+85°C          | 14 TSSOP-EP* | U14E-3          |  |

\*EP = Exposed pad.

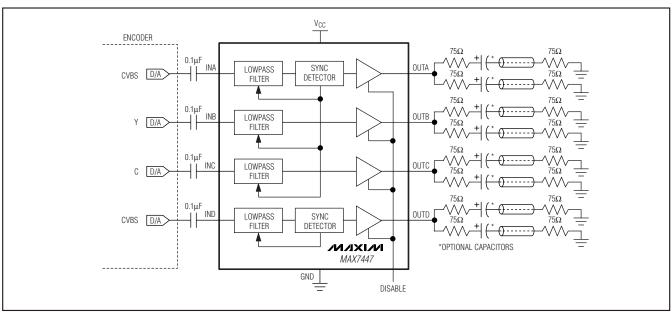

# **Functional Diagram**

Pin Configuration appears at end of data sheet.

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND+6V<br>All Other Pins to GND0.3V to (V <sub>CC</sub> + 0.3V) | Operating Temperature Range40°C to +85°C Storage Temperature Range65°C to +150°C |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Maximum Current into Any Pin Except VCC and GND±50mA                               | Junction Temperature+150°C                                                       |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                              | Lead Temperature (soldering, 10s)+300°C                                          |

| TSSOP-FP (denate 20.8mW/°C above ±70°C) 1667mW                                     |                                                                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5V \pm 5\%, C_L = 0 \text{ to 20pF}, R_L = 75\Omega \text{ to GND for DC-coupled load}, R_L = 75\Omega \text{ to } V_{CC} \text{ / 2 for AC-coupled load}, C_{IN\_} = 0.1 \mu\text{F}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted}. Typical values are at <math>V_{CC} = +5V, T_A = +25^{\circ}C.)$

| PARAMETER                    | SYMBOL            | CONDITIONS                                                           | MIN  | TYP  | MAX  | UNITS            |

|------------------------------|-------------------|----------------------------------------------------------------------|------|------|------|------------------|

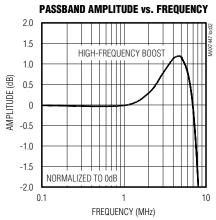

| Passband Response            |                   | f = 100kHz to 5MHz, relative to 100kHz                               | 0.9  | 1.2  | 1.5  | dB               |

| Stopband Attenuation         | AsB               | f ≥ 27MHz                                                            | 39   | 43   |      | dB               |

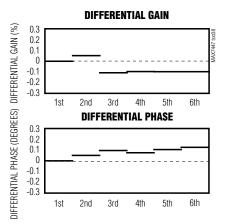

| Differential Gain            | dG                | 5-step modulated staircase                                           |      | 0.15 | 0.50 | %                |

| Differential Phase           | dθ                | 5-step modulated staircase                                           |      | 0.15 | 0.50 | Degrees          |

| Signal-to-Noise Ratio        | SNR               | Peak signal (2V <sub>P-P</sub> ) to RMS noise,<br>f = 100Hz to 50MHz |      | 80   |      | dB               |

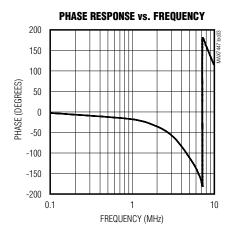

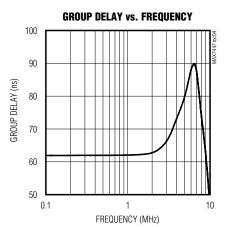

| Group Delay Deviation        | $\Delta t_{g}$    | Deviation from 100kHz to 4.1MHz                                      |      | 17   | 30   | ns               |

| Line-Time Distortion         | HDIST             | 18µs, 100 IRE bar                                                    |      |      | 0.3  | %                |

| Field-Time Distortion        | V <sub>DIST</sub> | 130 lines, 18µs, 100 IRE bar                                         |      |      | 0.5  | %                |

| Clamp Settling Time          | tCLAMP            | To ±1%                                                               |      | 430  |      | Lines            |

| Output DC Clamp Level        |                   | Channel A, B, D                                                      | 0.6  | 0.9  | 1.1  |                  |

|                              |                   | Channel C                                                            | 1.25 | 1.60 | 1.95 | V                |

| Low-Frequency Gain Accuracy  | Ay                | f = 100kHz, relative to a gain of +6dB                               | -3   |      | +3   | %                |

| Low-Frequency Gain Matching  | Av(match)         | Low-frequency channel-to-channel matching, f = 100kHz                |      |      | 4    | %                |

| Group Delay Matching         | tg(MATCH)         | Low-frequency channel-to-channel matching, f = 100kHz                |      | 2    |      | ns               |

| Channel-to-Channel Crosstalk | XTALK             | f = 100kHz to 3.58MHz                                                |      | 60   |      | dB               |

| Output Short-Circuit Current | Isc               | OUT_ shorted to GND or V <sub>CC</sub>                               |      | 70   |      | mA               |

| Input Leakage Current        | I <sub>IN</sub>   |                                                                      |      |      | 10   | μΑ               |

| Input Dynamic Swing          |                   | Channel A, B, D                                                      |      |      | 1.2  | V <sub>P-P</sub> |

|                              |                   | Channel C                                                            |      |      | 0.9  |                  |

| SUPPLY                       |                   |                                                                      |      |      |      |                  |

| Supply Voltage Range         | V <sub>C</sub> C  |                                                                      | 4.75 |      | 5.25 | V                |

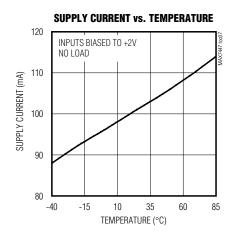

| Supply Current               | Icc               | No load                                                              |      | 100  | 140  | mA               |

| Power-Supply Rejection Ratio | PSRR              | $V_{IN} = 100 \text{mV}_{P-P}, f = 0 \text{ to } 3.5 \text{MHz}$     |      | 40   |      | dB               |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +5V \pm 5\%, C_L = 0 \text{ to } 20 pF, R_L = 75\Omega \text{ to GND for DC-coupled load}, R_L = 75\Omega \text{ to } V_{CC} \text{ / 2 for AC-coupled load}, C_{IN} = 0.1 \mu F, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted}. Typical values are at <math>V_{CC} = +5V, T_A = +25^{\circ}C.)$

| PARAMETER                        | SYMBOL               | CONDITIONS                                                              | MIN | TYP | MAX | UNITS |

|----------------------------------|----------------------|-------------------------------------------------------------------------|-----|-----|-----|-------|

| DISABLE                          |                      |                                                                         |     |     |     |       |

| Output Impedance During Disable  | Z <sub>DISABLE</sub> | At 5MHz                                                                 |     | 2   |     | kΩ    |

| Disable Logic-Input High Voltage | V <sub>IH</sub>      |                                                                         | 2.0 |     |     | V     |

| Disable Logic-Input Low Voltage  | VIL                  |                                                                         |     |     | 0.8 | V     |

| Disable Logic-Input Current      | IDISABLE             | V <sub>IL</sub> = 0V (sink), V <sub>IH</sub> = V <sub>CC</sub> (source) |     |     | ±10 | μΑ    |

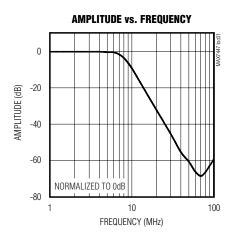

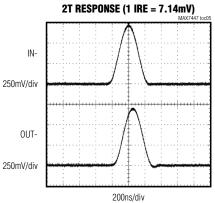

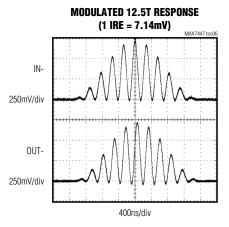

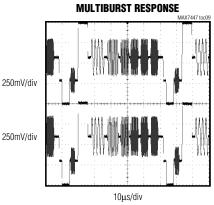

## Typical Operating Characteristics

$(V_{CC} = +5V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## Typical Operating Characteristics (continued)

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

# Pin Description

| PIN                                                                                                                    | NAME    | FUNCTION                                                                                                                                                             |  |

|------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                                                                                                      | INA     | Channel A Video Input. Use channel A for a CVBS video signal. AC-couple INA with a series 0.1µF capacitor.                                                           |  |

| 2                                                                                                                      | INB     | Channel B Video Input. Use channel B for the luma (Y) video signal. AC-couple INB with a series 0.1µF capacitor.                                                     |  |

| 3 INC Channel C Video Input. Use channel C for the chroma (C) video signal. AC-couple INC with a series 0.1 capacitor. |         | Channel C Video Input. Use channel C for the chroma (C) video signal. AC-couple INC with a series 0.1µF capacitor.                                                   |  |

| 4                                                                                                                      | IND     | Channel D Video Input. Use channel D for a second CVBS video signal. AC-couple IND with a series 0.1µF capacitor.                                                    |  |

| 5                                                                                                                      | DISABLE | Disable Logic Input. A logic-low on DISABLE enables the output buffers. A logic-high on DISABLE disables all output buffers and puts them in a high-impedance state. |  |

| 6–9                                                                                                                    | GND     | Ground                                                                                                                                                               |  |

| 10                                                                                                                     | Vcc     | +5V Supply Input                                                                                                                                                     |  |

| 11                                                                                                                     | OUTD    | Channel D Video Output. This output can be either AC- or DC-coupled.                                                                                                 |  |

| 12                                                                                                                     | OUTC    | Channel C Video Output. This output can be either AC- or DC-coupled.                                                                                                 |  |

| 13                                                                                                                     | OUTB    | Channel B Video Output. This output can be either AC- or DC-coupled.                                                                                                 |  |

| 14                                                                                                                     | OUTA    | Channel A Video Output. This output can be either AC- or DC-coupled.                                                                                                 |  |

# **Detailed Description**

The MAX7447 filters and buffers video-encoder DAC outputs in applications such as set-top boxes, hard-disk recorders, DVD players, and digital VCRs. The MAX7447 reconstructs and cleans up analog video signals from the output of DAC video encoders. Each channel consists of a lowpass filter and an output video buffer that drives two standard  $150\Omega$  video loads.

The MAX7447 is designed to process S-Video and CVBS video signals. The video signal processed by channel A (CVBS video signal) must include a sync pulse. This sync pulse provides the required timing for channels A, B, and C. Channel D allows an asynchronous CVBS video signal to be processed with its own local sync separator.

This device operates from a single +5V supply and has a nominal cutoff frequency of 5MHz optimized for NTSC, PAL, and SDTV.

#### **Filter**

#### Filter Response

The reconstruction filter consists of two 2nd-order Sallen-Key stages. The Butterworth-type response features a maximally flat passband for NTSC and PAL bandwidths. The stopband offers at least 43dB (typ) of attenuation at a video-encoder DAC sampling frequency of 27MHz and above (see the *Typical Operating Characteristics*).

#### High-Frequency Boost

Each channel has a +1.2dB high-frequency boost that increases image sharpness by compensating for signal degradation and rolloff in the video encoder.

#### **Output Buffers**

Each output buffer has a fixed gain of +6dB and can drive two  $150\Omega$  video loads with a  $2V_{P-P}$  signal. The MAX7447 can drive an AC load or drive the video load directly without using a large output capacitor. The output buffers drive DC loads with an output blanking level of less than 1V.

#### **Output Clamp Level**

When a sync pulse is detected on channel A (CVBS), the DC restore loop is activated for channels A, B, and C. Channel D's DC restore loop is activated by the sync pulse on channel D.The function of the loop is to set the DC level of the video signal to a specified voltage. See Table 1 for clamp levels and sync source.

**Table 1. Output Clamp Level and Sync Source**

| CHANNEL | CLAMP LEVEL (V) | SYNC SOURCE (V) |

|---------|-----------------|-----------------|

| А       | 0.8             | Channel A       |

| В       | 0.8             | Channel A       |

| С       | 1.6             | Channel A       |

| D       | 0.8             | Channel D       |

## Applications Information

#### **Input Considerations**

Use 0.1µF ceramic capacitors to AC-couple the inputs. These input capacitors store a DC level so the outputs are clamped to an appropriate DC voltage level.

#### **Output Considerations**

The outputs are typically connected to a 75 $\Omega$  series back-match resistor followed by the video cable. Because of the inherent divide-by-two of this configuration, the voltage on the video cable is always less than 1V, complying with industry-standard video requirements such as the European SCART standard (which allows up to 2V of DC on the video cable). The video buffer can also drive an AC-coupled video load. Good video performance is achieved with an output capacitor as low as 220 $\mu$ F.

#### **Power-Supply Bypassing and Layout**

The MAX7447 operates from a single +5V supply. Bypass  $V_{CC}$  to GND with a 0.1 $\mu$ F capacitor. Place all external components as close to the device as possible.

#### **Exposed Pads**

The TSSOP-EP package has an exposed pad on the bottom of the package. This pad is electrically connected to GND and should be connected to the ground plane for improved thermal conductivity. Do not route signals under this package.

#### Pin Configuration

# Chip Information

TRANSISTOR COUNT: 6300

PROCESS: BICMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.