#### M02171

# 11.3Gbps Dual Loop VCSEL Driver with Integrated Micro Controller

The M02171 is designed to drive vertical cavity surface emitting lasers used in Transmitter optical sub-assemblies and supports data rates up to 11.3 Gbps. The M02171 supports both common anode and common cathode VCSEL configurations. It combines the diagnostic monitoring Interface compliant with SFP, XFP, SFP+ and a driver compatible with VCSEL lasers in a compact 5mm x 5mm QFN package.

The M02171 features dual loop control, which compensates for changes in laser slope efficiency over temperature and life. These features can also reduce or eliminate temperature calibration, thus improving system reliability and reducing overall cost. Integrated safety circuitry provides latched bias and modulation current shutdown if a fault condition is detected and provides either internal V<sub>CC</sub> switch or ground switch. The device comes with firmware required for diagnostic monitoring, offering a seamless interface for calibration and setup.

Other available solutions: M02170 - 11.3Gbps Dual Loop DML Driver with Integrated Micro Controller M02172 - 11.3Gbps EML Driver with Integrated Micro Controller

#### **Features**

- Data Rates to 11.3 Gbps. Single 3.3V supply

- Dual Loop Control for average optical power and modulation amplitude

- · Programmable VCSEL bias current to 15mA

- Programmable VCSEL modulation current to 15mA

- Integrated mode supports SFF-8472/SFP/SFP+ Requirements

- External micro controller mode supports SFF-8472/XFP/SFP/SFP+ requirements

- · SFP/XFP compliant safety circuitry

- · Provides internal Vcc and ground switch for single point faults

- · Input equalization for SFP+ requirements

- 2-wire or SPI serial interface available

- Programmable GPIO, selectable 6 bit or 10 bit DAC via serial interface

- Five user configurable General purpose I/Os

- Two available auxiliary 12 bit ADC inputs

- Provides complete Calibration and Firmware setup

- 54 mA typical supply current

- Operating Temperature: -40 °C to +95 °C

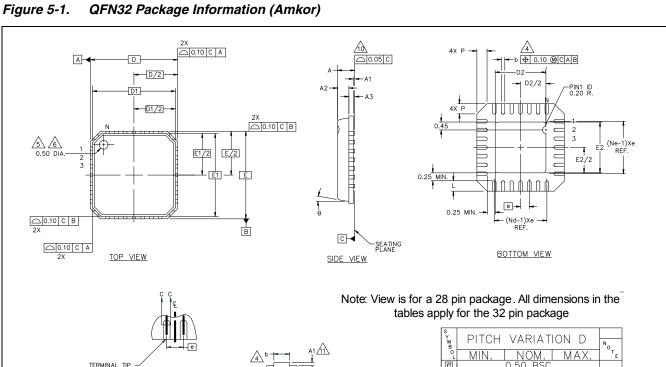

- 5mm x 5mm QFN package

#### **Applications**

- IEEE802.3 10GBASE-SR

- SFP/SFP+/XFP MSA Modules

- 8G Fiber Channel Modules

- SONET OC-192 Optical Transmitters

- SDH STM-64 Optical Transmitters

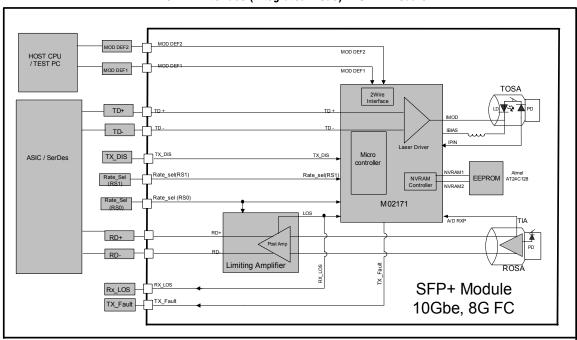

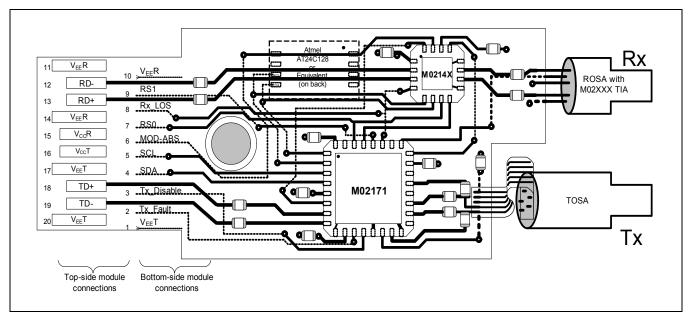

#### M02171 Interface (Integrated Mode) in SFP+ Module

# **Ordering Information**

| Part Number                                                                                                                        | Package               | Operating Temperature |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|--|--|--|--|

| M02171G-12*                                                                                                                        | 32 pin, 5mm x 5mm QFN | -40°C to +95°C        |  |  |  |  |

| *The G in the part number indicates that this is an RoHS compliant package. Refer to www.mindspeed.com for additional information. |                       |                       |  |  |  |  |

# **Revision History**

| Revision | Level   | Date          | ASIC<br>Revision | Description                                                                                                                                                                        |

|----------|---------|---------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E        | Release | December 2010 | -12              | Update Ordering Information. Remove 8k EEPROM download option as it is not required to meet the SFP t_init and t_serial timing requirements.  Update package diagram measurements. |

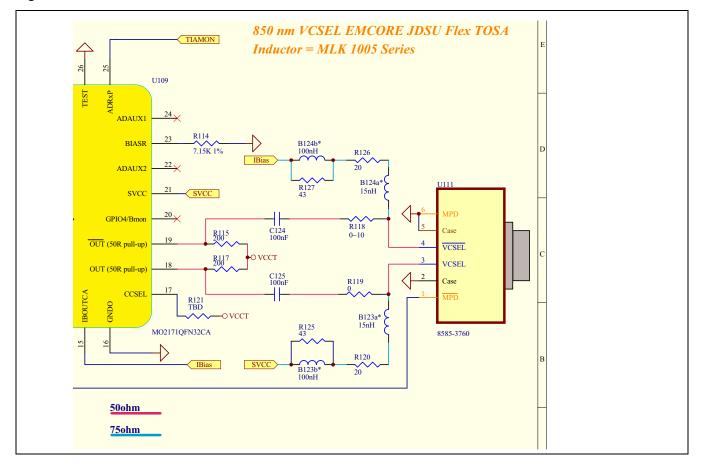

| D        | Release | May 2009      | -12              | Final characterization results included in specifications. Applications figure added for Emcore and JDSU TOSAs. Minor corrections made to text explanations.                       |

| С        | Advance | April 2007    | -11P             | Added SPI, Functional description and Applications information                                                                                                                     |

| В        | Advance | March 2007    | -11P             | Change Pins 9,10 and 29, updated drawings to include changes to SFP+                                                                                                               |

| А        | Advance | January 2007  | -11P             | Initial                                                                                                                                                                            |

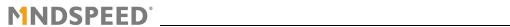

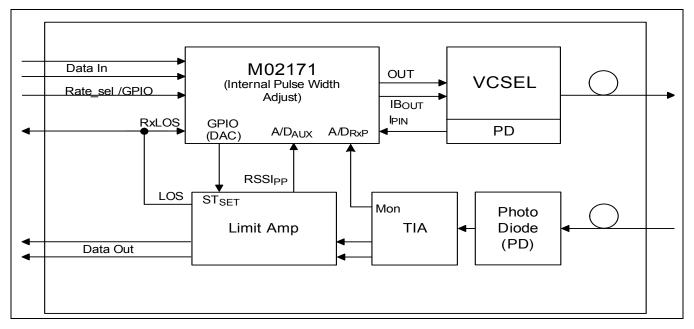

#### M02171 Block Diagram

# 1.0 Product Specification

# 1.1 Absolute Maximum Ratings

These are the absolute maximum ratings at or beyond which the IC can be expected to fail or be damaged. Reliable operation at these extremes for any length of time is not implied.

Table 1-1. Absolute Maximum Ratings

| Symbol                   | Parameter                                                          | Rating       | Units            |

|--------------------------|--------------------------------------------------------------------|--------------|------------------|

| V <sub>CC</sub>          | 3.3 V power supply voltage                                         | -0.4 to +4.0 | V                |

| T <sub>A</sub>           | Operating Ambient Temperature                                      | -40 to +95   | °C               |

| T <sub>STG</sub>         | Storage temperature                                                | -65 to +150  | °C               |

| IBOUT <sub>CA(MAX)</sub> | Maximum bias output current at IBOUT <sub>CA</sub>                 | 25           | mA               |

| IBOUT <sub>CC(MAX)</sub> | Maximum bias output current at IBOUT <sub>CC</sub>                 | 25           | mA               |

| I <sub>MOD(MAX)</sub>    | Max. modulation current - common anode or common cathode operation | 25           | mA <sub>PP</sub> |

# 1.2 Recommended Operating Conditions

Table 1-2. Recommended Operating Conditions

| Parameter                           | Rating     | Units |

|-------------------------------------|------------|-------|

| Power supply (V <sub>CC</sub> -GND) | 3.3 ±5%    | V     |

| Operating ambient                   | -40 to +95 | °C    |

# 1.3 DC Characteristics

$V_{CC}$  = 3.05 to 3.55V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C,  $I_{MOD}$  = 5mA,  $I_{BIAS}$  = 5mA, unless otherwise noted.

Table 1-3. DC Characteristics

| Symbol                        | Parameter                                                            | Conditions                                                                                         | Minimum               | Typical               | Maximum         | Units |

|-------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------|-------|

| V <sub>CC</sub>               | V <sub>CC</sub> operating voltage                                    |                                                                                                    | 3.05                  | 3.3                   | 3.55            | V     |

| I <sub>CC</sub>               | I <sub>CC</sub> supply current <sup>(1)</sup>                        | High-rate mode Low-rate mode Increase due to enabling Pulse Width Adjust                           | -<br>-<br>-           | 54<br>42<br>2         | 84<br>_<br>_    | mA    |

| I <sub>CC_DIS</sub>           | I <sub>CC</sub> when part Disabled                                   | Device is in disabled                                                                              | _                     | 36                    | 48              | mA    |

| V <sub>CCTHL</sub>            | 3.3 V supply detection (low voltage) threshold                       | Minimum of either V <sub>CC</sub> supply low detection voltage or internal Power on Reset voltage  | -                     | 2.6                   | 2.85            | V     |

| V <sub>CCTHH</sub>            | 3.3 V supply detection (high voltage) threshold                      |                                                                                                    | 3.55                  | 3.8                   | 4.00            | V     |

| V <sub>FAULTL</sub>           | Low fault voltage detection threshold (IBOUT <sub>CA</sub> , BIAS_R) | Fault condition occurs when voltage drops below this level                                         | _                     | 400                   | 600             | mV    |

| V <sub>FAULTH</sub>           | High fault voltage detection threshold (IBOUT <sub>CC</sub> )        | Fault condition occurs when voltage exceeds this level                                             | V <sub>CC</sub> - 0.6 | V <sub>CC</sub> - 0.4 | -               | V     |

| I <sub>BIAS_CA</sub>          | Bias current adjust range CA <sup>(2)</sup>                          | At IBOUT <sub>CA</sub> , V(IBOUT <sub>CA</sub> ) > 0.7 V                                           | 3                     | -                     | 15              | mA    |

| I <sub>BIAS_CC</sub>          | Bias current adjust range CC                                         | At IBOUT <sub>CC</sub> ., V(IBOUT <sub>CC</sub> ) < 2.5 V                                          | 1                     | -                     | 15              | mA    |

| I <sub>BIAS(OFF)_</sub><br>CA | Bias current with output disabled                                    | $TX_DIS = high and/or SOFT DIS = high;$<br>$V(IBOUT_{CA}) = V_{CC}$ for common anode               | _                     | 300                   | 600             | μА    |

| I <sub>BIAS(OFF)_</sub><br>CC | Bias current with output disabled                                    | TX_DIS = high and/or SOFT DIS = high;<br>V(IBOUT <sub>CC</sub> )= 0V for common cathode            | _                     | 5                     | 150             | μА    |

| BIAS <sub>RATIO</sub><br>CC   | Ratio of bias current to BIAS <sub>MON</sub> current                 | V(IBOUT <sub>CC</sub> )= 2.0 V                                                                     | 13.6                  | 14.8                  | 15.8            | A/A   |

| BIAS <sub>RATIO</sub><br>CA   | Ratio of bias current to BIAS <sub>MON</sub> current                 | V(IBOUT <sub>CA</sub> )= 1.5 V                                                                     | 13.6                  | 14.8                  | 15.8            | A/A   |

| $V_{MD}$                      | Monitor diode reverse bias voltage                                   | Minimum is with maximum I <sub>PIN</sub> current, maximum is with zero I <sub>PIN</sub> current    | 1.5                   | 2.0                   | V <sub>CC</sub> | V     |

| I <sub>MD</sub>               | Monitor diode current adjustment range <sup>(3)</sup>                | For stable APC loop operation                                                                      | 10                    | -                     | 1400            | μА    |

| C <sub>MDMAX</sub>            | Maximum monitor photodiode capacitance <sup>(3)</sup>                | For stable APC loop operation in analog closed mode; includes any additional parasitic capacitance | _                     | -                     | 100             | pF    |

| V <sub>IH_DIS</sub>           | TTL/CMOS input high voltage<br>(TX_DIS, Pwdn/Rst, SPI_sel, Test)     |                                                                                                    | 2.0                   | -                     | V <sub>CC</sub> | V     |

| $V_{IL\_DIS}$                 | TTL/CMOS input low voltage (TX_DIS, Pwdn/Rst, SPI_sel, Test)         |                                                                                                    | 0                     | -                     | 0.8             | V     |

| $V_{IH\_SEL}$                 | CC <sub>SEL</sub> CMOS input high voltage                            |                                                                                                    | 2.4                   | -                     | -               | V     |

| $V_{IL\_SEL}$                 | CC <sub>SEL</sub> CMOS input low voltage                             |                                                                                                    | -                     | -                     | 1.0             | V     |

| V <sub>IH_I0</sub>            | GPIO input high voltage                                              |                                                                                                    | 2.0                   | -                     | V <sub>CC</sub> | V     |

| V <sub>IL_I0</sub>            | GPIO input low voltage                                               | When configured as a digital input                                                                 | 0                     | -                     | 1.0             | V     |

|                               |                                                                      |                                                                                                    |                       |                       |                 |       |

Table 1-3. DC Characteristics

| Symbol                | Parameter                                           | Conditions                                                                              | Minimum               | Typical               | Maximum                                      | Units |

|-----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------------------------------|-------|

| I <sub>LK_I0_04</sub> | GPIO 0-4 leakage current                            | When configured as a tristated digital input                                            | -10                   | 0                     | 10                                           | μА    |

| V <sub>IH_LOS</sub>   | LOS input high voltage                              |                                                                                         | 2.0                   | -                     | V <sub>CC</sub>                              | V     |

| $V_{IL\_LOS}$         | LOS input low voltage                               |                                                                                         | 0                     | -                     | 0.8                                          | V     |

| V <sub>OH_FAIL</sub>  | Logic output high voltage (FAIL)                    | With external 10 k $\Omega$ pull-up to V $_{CC}$                                        | V <sub>CC</sub> - 0.6 | -                     | -                                            | V     |

| V <sub>OL_FAIL</sub>  | Logic output low voltage (FAIL)                     | I <sub>OL</sub> = 1.2 mA                                                                | -                     | -                     | 0.4                                          | V     |

| V <sub>OH_IO</sub>    | GPIO output high voltage                            | When configured as a digital output $I_{OH} = -2$ mA.                                   | 2.4                   | _                     | V <sub>CC</sub>                              | V     |

| V <sub>OL_IO</sub>    | GPIO output low voltage                             | When configured as a digital output I <sub>OL</sub> = 2 mA                              | 0                     | -                     | 0.4                                          | V     |

| R <sub>IN</sub>       | Differential input resistance                       |                                                                                         | 85                    | 100                   | 115                                          | Ω     |

| R <sub>OUT</sub>      | Output resistance                                   |                                                                                         | 45                    | 55                    | 65                                           | Ω     |

| V <sub>CMSELF</sub>   | Self-biased common mode input voltage               |                                                                                         | -                     | V <sub>CC</sub> - 1.3 | -                                            | V     |

| V <sub>INCM</sub>     | Common-mode input compliance voltage <sup>(3)</sup> | Data inputs                                                                             | V <sub>CC</sub> - 1.5 | _                     | V <sub>CC</sub><br>-V <sub>IN(Diff)</sub> /4 | V     |

| V <sub>IN(Diff)</sub> | Differential input voltage (3)                      | Peak to Peak, Equalizer off                                                             | 80                    | -                     | 1000                                         | mV    |

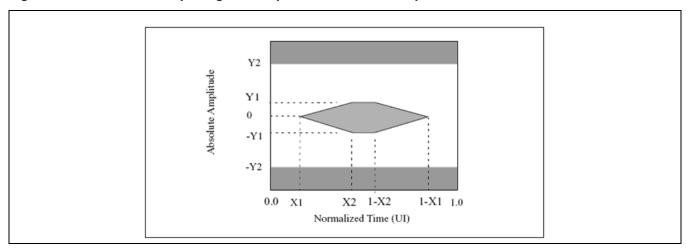

|                       |                                                     | For SFP+ applications. (Refer to the Signal compliance mask in Figure 1-1) Equalizer on |                       |                       |                                              |       |

|                       |                                                     | X1:SFP+ Eye Mask compliance                                                             |                       |                       | 0.14                                         | UI    |

|                       |                                                     | X2: SFP+ Eye Mask compliance                                                            |                       |                       | 0.35                                         | UI    |

|                       |                                                     | Y1:SFP+ Eye Mask compliance                                                             | 75                    |                       |                                              | mV    |

|                       |                                                     | Y2: SFP+ Eye Mask compliance                                                            |                       |                       | 400                                          | mV    |

#### NOTES:

- 1. Excludes bias and modulation currents delivered to the laser.

- 2. To meet  ${\rm BIAS_{RATIO}}$  CA specifications. Operation as low as 1 mA is achievable.

- 3. Guaranteed by design and characterization.

Figure 1-1. Differential Input signal Compliance mask at the input of the M02171

# 1.4 AC Characteristics

$V_{CC}=3.05$  to 3.55V,  $T_A=-40^{\circ}C$  to +95°C, unless otherwise noted. Typical values are  $V_{CC}=3.3$ V,  $T_A=25^{\circ}C$ ,  $I_{MOD}=5$ mA,  $I_{BIAS}=5$ mA, unless otherwise noted. All values measured with the input equalizer on and using 6 inches (15 cm) of FR4 non-backdrilled stripline trace length.

Table 1-4. AC Characteristics

| Symbol                          | Parameter                                                 | Conditions                                                                        | Minimum | Typical           | Maximum | Units             |

|---------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------|---------|-------------------|---------|-------------------|

| I <sub>MOD</sub>                | Modulation current adjust range                           | Current delivered to VCSEL assuming a series resistance between 40 - 110 $\Omega$ | 5       | ı                 | 15      | mA <sub>PP</sub>  |

| I <sub>MOD(OFF)</sub>           | Modulation current with output disabled                   | TX_DIS = high and/or SOFT_DIS = high                                              | -       | 15                | 150     | μА                |

| I <sub>MOD_RATIO</sub>          | Ratio of modulation current to MOD <sub>MON</sub> current | = (I <sub>OUTP</sub> - I <sub>OUTN</sub> )/I <sub>MODMON</sub>                    | _       | 12.5              | -       | A/A               |

| PWA                             | Pulse width adjustment range                              | 50% crossing point at DAC mid range                                               | -       | ±20               | -       | ps                |

| t <sub>R</sub> / t <sub>F</sub> | Modulation output rise / fall times                       | 20% to 80% into $50\Omega$ load. Measured                                         | -       | 21 <sup>(1)</sup> | 29      | ps                |

|                                 |                                                           | using alternating 1-0 pattern at 2.5 Gbps                                         |         | 30 (2)            | 60      | ps                |

| 0S                              | Overshoot of modulation output                            | Into $50\Omega$ load                                                              | -       | 3                 | -       | %                 |

| RJ                              | Random jitter                                             | Measured by 7.5 GHz Bessel filter at output                                       | _       | 0.4               |         | ps <sub>RMS</sub> |

| DJ                              | Modulation output deterministic jitter <sup>(3)</sup>     | Peak-to-peak into $50\Omega$ load using $2^{15}$ - 1 PRBS at 10.3 Gbps            | -       | 9                 | 17      | ps                |

#### NOTES:

- . With RS1=1, For Tx Signalling rates > 4.25Gb/s

- 2. With RS1=0, For Tx Signalling rates  $\leq 4.25 Gb/s$

- 3. Includes Duty Cycle Distortion

# 1.5 Soft Control Timing Management

$V_{CC}$  = 3.05 to 3.55V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C unless otherwise noted using internal micro controller.

Table 1-5. I/O Timing for Soft Control and Status Functions

| Symbol     | Parameter                                       | Conditions                                                                                     | Тур | Max | Units |

|------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|-----|-----|-------|

| t_off      | Tx_DIS assert time                              | Time from TX_DIS bit set <sup>(1)</sup> until optical output falls below 10% of nominal        | -   | 100 | ms    |

| t_on       | TX_DIS deassert time                            | Time from TX_DIS bit cleared <sup>(1)</sup> until optical output rises above 90% of nominal    | _   | 100 | ms    |

| t_init     | Time to initialize, including reset of TX_Fault | Time from power on or negation of TX_FAULT using TX_DISABLE until transmitter output is stable |     | 300 | ms    |

| t_fault    | TX_Fault assert time                            | Time from fault to TX_FAULT bit set                                                            |     | 100 | ms    |

| t_loss_on  | RX_LOS assert time                              | Time from LOS state to RX_LOS bit set                                                          |     | 100 | ms    |

| t_loss_off | LOS deassert time                               | Time from non-LOS state to RX_LOS bit cleared                                                  |     | 100 | ms    |

| t_serial   | Serial bus hardware ready                       | Time from power on until host can read from the serial bus                                     |     | 300 | ms    |

#### NOTE:

<sup>1.</sup> Measured from falling clock edge after stop bit of write transaction

# 1.6 Monitors ADC Specifications

$V_{CC}$  = 3.05 to 3.55V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C unless otherwise noted.

Table 1-6. A/D Electrical Specifications

| lanut                        | Tuno                          | Range   |         |       |         | Accuracy |       |         |

|------------------------------|-------------------------------|---------|---------|-------|---------|----------|-------|---------|

| Input                        | Туре                          | Minimum | Maximum | Units | Minimum | Maximum  | Units | Notes   |

| Tx Power Monitor             | (Internal)<br>Current Sinking | 10      | 1400    | μА    | -10     | +10      | %     | 1,2,3   |

| Bias Current Monitor         | (Internal)<br>Current Sinking | 10      | 1400    | μА    | -10     | +10      | %     | 1,2,3   |

| Modulation Current Monitor   | (Internal)<br>Current Sinking | 10      | 1400    | μА    | -10     | +10      | %     | 1,2,3   |

| Rx Power Monitor             | (External)<br>Current Sinking | 3       | 1400    | μА    | -10     | +10      | %     | 1,2,3,4 |

|                              | Voltage mode                  | 0       | 2.3     | V     | -15     | +15      | mV    | 2,8,9   |

| Power Supply Monitor         | (Internal)<br>Voltage         | 2.85    | 3.6     | V     | -25     | +25      | mV    | 2,6     |

| Internal Temperature Monitor | (Internal)<br>Temperature     | -40     | +105    | °C    | -3      | +3       | °C    | 2,7     |

|                              | Current Sinking               | 10      | 1400    | μΑ    | -10     | +10      | %     | 1,2,3,4 |

| AUX1, AUX2                   | Current Sourcing              | 10      | 1400    | μА    | -10     | +10      | %     | 1,2,4,5 |

|                              | Voltage                       | 0       | 2.3     | V     | -15     | +15      | mV    | 2,8,9   |

| Update Rate                  | All ADCs                      | 1       |         | kHz   | _       | -        | -     | -       |

#### NOTES:

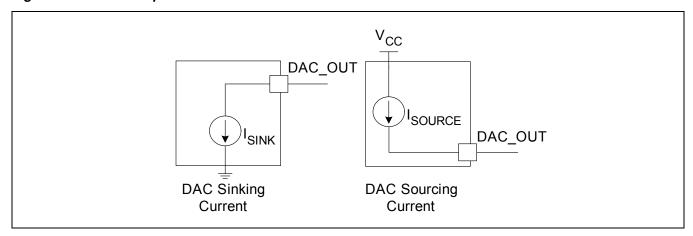

- 1. For definition of sourcing and sinking see Figure 1-2.

- 2. Module calibration required for valid units.

- 3. Code 000h means 0 µA, code FFFh means 1600 µA when sinking current. However, the result is only valid in the range specified.

- 4. Minimum value of monitored current is achieved with internal digital filter (default setting).

- 5. Code 000h means 0 µA, code FFFh means 1500 µA when sourcing current. However, the result is only valid in the range specified

- 6. Code 000h means 0 V, code FFFh means 6.55 V. However, the supply monitoring value is only valid in the range specified.

- 7. ADC output will be offset binary. Code 000h means the lowest temperature the ADC can measure, while FFFh means the highest temperature the ADC can measure.

- 8. Input impedance of ADC is larger than 100 k $\Omega$ .

- 9. Code 000h means 0 V, code FFFh means 2.3 V. However, the result is only valid in the range specified.

# 1.7 DAC Specifications

$V_{CC}$  = 3.05 to 3.55V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C unless otherwise noted.

# 1.7.1 Bias and Modulation Current DAC Specifications

Table 1-7. Laser Driver Bias and Modulation Current D/A

| Parameter  | Minimum | Typical | Maximum | Units |

|------------|---------|---------|---------|-------|

| Resolution | _       | 12      | -       | bits  |

# 1.7.2 Internal 6 bit DAC (PWA and BMON\_MAG) Specifications

Table 1-8. Internal 6 bit DAC<sup>(1)</sup>

| Parameter                                | Minimum | Typical | Maximum | Units |

|------------------------------------------|---------|---------|---------|-------|

| Resolution                               | -       | 6       | -       | bits  |

| Full scale output (current sinking)      | 1.01    | _       | 1.13    | mA    |

| Linearity                                |         |         |         |       |

| DNL                                      | -1      | -       | +1      | LSB   |

| INL                                      | -1      | _       | +1      | LSB   |

| Offset                                   | -5      | _       | +5      | μА    |

| Settling time                            | -       | 10      | _       | μS    |

| Compliance (voltage for sinking current) | 1.1     | _       | 2.6     | V     |

| NOTE:                                    | •       |         |         | •     |

<sup>1.</sup> The pulse width adjust DAC is mapped to GPIO(2) and the BMON\_MAG DAC is mapped to GPIO(4).

Figure 1-2. DAC Output Definitions

# 1.7.3 General Purpose 6 bit DAC Specifications

Table 1-9. General Purpose 6 bit DAC (1)

| Parameter                                               | Minimum | Typical | Maximum | Units |

|---------------------------------------------------------|---------|---------|---------|-------|

| Resolution                                              | -       | 6       | -       | bits  |

| Full scale output current (current sourcing or sinking) | 1.01    | 1.07    | 1.13    | mA    |

| Linearity                                               |         |         |         |       |

| DNL                                                     | -1      | _       | +1      | LSB   |

| INL                                                     | -1      | _       | +1      | LSB   |

| Offset                                                  |         |         |         |       |

| Current source                                          | _       | _       | +5      | μΑ    |

| Current sink                                            | -5      | -       | +5      | μΑ    |

| Settling time                                           | _       | 10      | _       | μS    |

| Voltage Compliance                                      |         |         |         |       |

| Current source                                          | 0       | -       | 1.1     | V     |

| Current sink                                            | 1.1     | -       | 2.6     | V     |

| NOTE:                                                   | 1       | 1       | 1       |       |

<sup>1.</sup> The General purpose 6 bit DAC is mapped to GPIO(1).

# 1.7.4 General Purpose 10 bit DAC Specification

Table 1-10. General Purpose 10 bit DAC (1,4)

| Parameter                                    | Minimum | Typical | Maximum | Units |

|----------------------------------------------|---------|---------|---------|-------|

| Resolution                                   | -       | 10      | -       | bits  |

| Voltage Mode Operation <sup>(2)</sup>        |         | 1       | 1       |       |

| Full scale output voltage                    | 1.37    | 1.45    | +1.53   | V     |

| Linearity                                    |         |         |         |       |

| DNL                                          | -1      | _       | +1      | LSB   |

| INL                                          | -4      | -       | +4      | LSB   |

| Offset                                       | -       | -       | +1.5    | mV    |

| Settling time                                | -       | 10      | -       | μS    |

| Output Resistance                            | 0.8     | 1       | 1.2     | kΩ    |

| Current Mode Operation <sup>(2, 3)</sup>     |         | 1       | 1       | l     |

| Full scale output current (current sourcing) | 1.40    | 1.48    | +1.56   | mA    |

| Linearity                                    |         |         |         |       |

| DNL                                          | -1      | -       | +1      | LSB   |

| INL                                          | -4      | _       | +4      | LSB   |

| Offset                                       | -       | -       | +1.5    | μА    |

Table 1-10. General Purpose 10 bit DAC (1,4)

| Parameter                                 | Minimum | Typical | Maximum | Units |

|-------------------------------------------|---------|---------|---------|-------|

| Settling time                             | _       | 10      | -       | μS    |

| Compliance (voltage for sourcing current) | 0       | -       | 1.1     | V     |

#### NOTES:

- 1. The General Purpose 10 bit DAC is mapped to GPIO(0).

- 2. Output may either be a current or a voltage. User selectable.

- 3. In current mode, DAC output can only source current. See Figure 1-2.

# 1.8 Inrush Current Specification

$V_{CC}$  = 3.05 to 3.55V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C unless otherwise noted.

Table 1-11. XFP/SFP+ POR Characteristics

| Parameter                                                       |      | Minimum | Typical | Maximum | Units |

|-----------------------------------------------------------------|------|---------|---------|---------|-------|

| I <sub>CC</sub> Peak Inrush (I <sub>CC—peak</sub> )             |      | _       | _       | 50      | %     |

| I <sub>CC</sub> Ramp rate (dI <sub>CC</sub> /dt) <sup>(1)</sup> | SFP+ |         |         | 50      | mA/μs |

|                                                                 | XFP  |         |         | 100     | mA/μs |

#### NOTE:

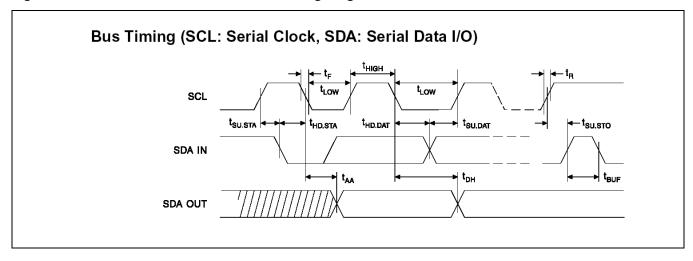

# 1.9 Host two-wire Timing Specifications

(MODDEF(1)/SCL and MODDEF(2)/SDA) (Standard Mode or Fast Mode two-wire serial) and NVRAM Controller Timing Specifications (NVRAM1 (SDA) AND NVRAM2 (SCL)) (Fast Mode two-wire serial)

$V_{CC}$  = 3.05 to 3.55V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C unless otherwise noted.

Table 1-12. Host and NVRAM Controller Timing Specifications (see Figure 1-3)

| Symbol                 | Parameter                                                     | Conditions | Minimum | Typical | Maximum | Units |

|------------------------|---------------------------------------------------------------|------------|---------|---------|---------|-------|

| f <sub>SCL_HOST</sub>  | Clock Frequency, SCL <sup>(1)</sup>                           |            | -       | -       | 400     | kHz   |

| f <sub>SCL_NVRAM</sub> | Clock Frequency, SCL                                          |            | 530     | -       | 900     | kHz   |

| t <sub>LOW</sub>       | Clock Pulse Width Low                                         |            | 1.3     | -       | -       | μS    |

| t <sub>HIGH</sub>      | Clock Pulse Width High                                        |            | 1.0     | -       | -       | μS    |

| t <sub>AA</sub>        | Clock Low to Data Out Valid                                   |            | 0.05    | -       | 0.9     | μS    |

| t <sub>BUF</sub>       | Time the bus must be free before a new transmission can start |            | 1.3     | -       | -       | μS    |

| t <sub>HDSTA</sub>     | Start Hold Time                                               |            | 0.6     | -       | -       | μS    |

<sup>1.</sup> Excludes external capacitors. Modules which present a small capacitive load to the host during hotplug are exempt from the inrush current requirements since they limit the total in rush charge.

Table 1-12. Host and NVRAM Controller Timing Specifications (see Figure 1-3)

| Symbol                  | Parameter                                                       | Conditions                                                                                     | Minimum | Typical | Maximum | Units |

|-------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| t <sub>SUSTA</sub>      | Start Set-up Time                                               |                                                                                                | 0.6     | -       | _       | μS    |

| t <sub>HDDAT</sub>      | Data In Hold Time                                               |                                                                                                | 3       | -       | _       | ns    |

| t <sub>SUDAT</sub>      | Data In Set-up Time                                             |                                                                                                | 100     | -       | _       | ns    |

| t <sub>SUSTO</sub>      | Stop Set-up Time                                                |                                                                                                | 0.6     | -       | _       | μS    |

| t <sub>f_HOST</sub>     | Host Output fall time <sup>(2)</sup>                            | 20-80%. Capacitive load for each bus line = 10 to 400 pF; $R_{PULL-UP}$ = 4.7 to 10 k $\Omega$ | _       | -       | 100     | ns    |

| R <sub>PULL-UP_EE</sub> | Outputs (NVRAM1 and NVRAM2) internal pull-up resistor value (3) |                                                                                                | _       | 8       | _       | kΩ    |

| t <sub>f_NVRAM</sub>    | NVRAM Controller Output fall time <sup>(3)</sup>                | 20-80%. No external pull-up resistor; 13 pf loading                                            | -       | -       | 50      | ns    |

| t <sub>r_NVRAM</sub>    | NVRAM Controller Output rise time <sup>(3)</sup>                | 20-80%. No external pull-up resistor; 13 pf loading                                            | -       | _       | 300     | ns    |

|                         | Time bus must be free before a new transmission start.          | Between STOP and START                                                                         | 20      |         |         | μS    |

| t <sub>DH</sub>         | Data Out Hold Time                                              |                                                                                                | 50      | _       | -       | ns    |

#### **NOTES:**

- 1. The host two wire bus is fully compliant with SFP timing requirements to run at 400 kHz.

- 2. For the host interface, the output rise time is determined by user selection of  $R_{PULL-UP}$  and the total line capacitance.

- 3. NVRAM two-wire bus only. Since the M02171 NVRAM1/NVRAM2 is a dedicated two-wire serial bus to the external EEPROM, the M02171 internally includes R<sub>PULL-UP</sub> to eliminate adding these extra external components.

Figure 1-3. Host and NVRAM Controller Timing Diagrams

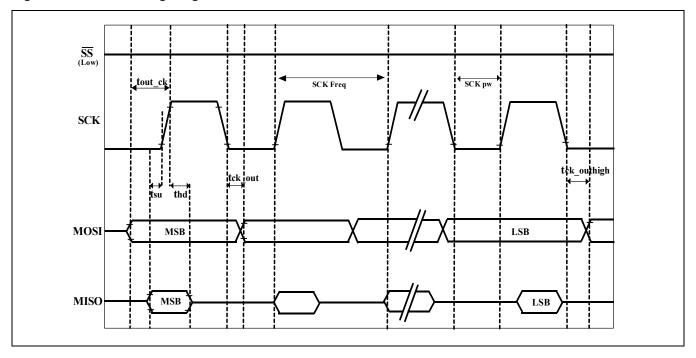

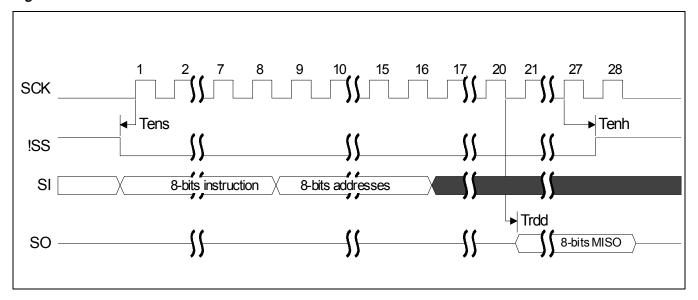

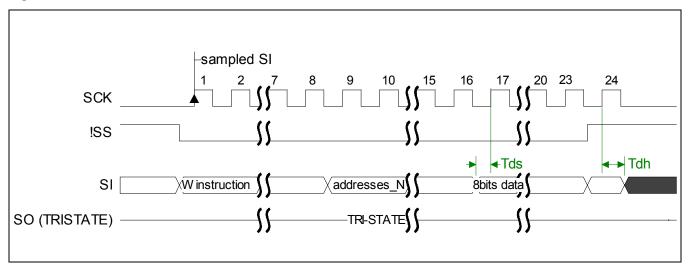

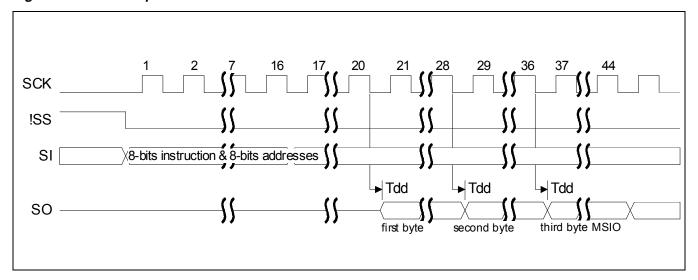

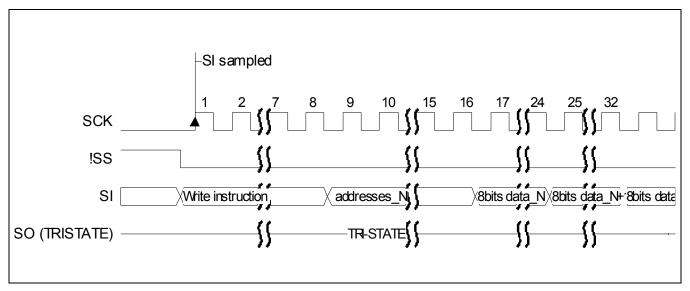

# 1.10 SPI Electrical Timing Specifications

$V_{CC}$  = 3.05 to 3.55V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C unless otherwise noted.

Table 1-13. SPI Electrical Timing Specifications

| Symbol                  | Parameter          | Min | Тур                    | Max | Units |

|-------------------------|--------------------|-----|------------------------|-----|-------|

|                         | SPI_CK Frequency   |     |                        | 10  | MHz   |

|                         | SPI_CK Pulse Width |     | 50% duty cycle         |     | %     |

|                         | Rise/Fall time     |     | 3.6                    |     | ns    |

| t <sub>su</sub>         | Setup time         |     | 10                     |     | ns    |

| t <sub>hd</sub>         | Hold time          |     | 10                     |     | ns    |

| t <sub>out_ck</sub>     | Out to SPI_CK      |     | 0.5 x t <sub>sck</sub> |     | ns    |

| t <sub>ck_out</sub>     | SPI_CK to Out      |     | 10                     |     | ns    |

| t <sub>ck_outhigh</sub> | SPI_CK to Out high |     | 10                     |     | ns    |

Figure 1-4. SPI Timing Diagram. External controller is Master and M02171 is Slave

# 1.11 Control and Status I/O Timing

$V_{CC}$  = 3.05 to 3.55V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C unless otherwise. Timing values are for hardware pins.

Table 1-14. Timing Requirements of SFP/XFP/SFP+ Control and Status I/O

| Symbol                | Parameter                                       | Conditions                                                                                        | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| t_off                 | TX_DIS assert time                              | Rising edge of TX_DIS to fall of output signal below 10% of nominal                               |         | -       | 10      | μS    |

| t_on                  | TX_DIS negate time                              | Falling edge of TX_DIS to rise of output signal above 90% of nominal                              |         | -       | 1       | ms    |

| t_init <sup>(1)</sup> | Time to initialize, including reset of TX_Fault | Time from power on or negation of Tx_Fault using TX_DIS until laser driver output is stable       |         | -       | 300     | ms    |

| t_fault               | TX_Fault assert time                            | From occurrence of fault condition to TX_Fault high                                               |         | -       | 100     | μS    |

| t_reset               | TX_DIS time to start reset                      | Time TX_DIS must be held high to reset TX_Fault. TX_DIS pulse width required to initialize safety |         |         | 10      | μS    |

|                       |                                                 | circuitry or reset a latched fault.                                                               |         |         |         |       |

| P-Down/<br>RST_on     | P_Down /RST assert delay                        | From power down initiation                                                                        |         |         | 100     | μ\$   |

|                       | P_Down reset time                               | Min length of P_down assert to initiate reset                                                     | 10      |         |         | μS    |

#### NOTE:

<sup>1.</sup> From power on or hotplug after supply OK or from falling edge of P\_Down/Rst

# 2.0 Pin Definitions

Table 2-1. Pin Descriptions

| QFN Pin<br>Number | Name                      | Function                                                                                                                                                                                                                            |

|-------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | NVRAM1 (SDA)              | SDA interface to external EEPROM (internally pulled up to $V_{CC}$ with 8 $k\Omega$ )                                                                                                                                               |

| 2                 | NVRAM2 (SCL)              | SCL interface to external EEPROM (internally pulled up to $V_{CC}$ with 8 $k\Omega$ )                                                                                                                                               |

| 3                 | MODDEF(1)/<br>SPI_0       | For 2-wire: MODDEF1 is the serial clock For SPI: SPI_O is slave output                                                                                                                                                              |

| 4                 | MODDEF(2)/<br>SPI_I       | For 2-wire: MODDEF2 is the serial data For SPI: SPI_I is slave input                                                                                                                                                                |

| 5                 | V <sub>CC</sub>           | 3.3V power supply.Connect to 3.3V                                                                                                                                                                                                   |

| 6                 | Pwdn/Rst                  | Control input. 60 k $\Omega$ internal pull up to $V_{CC}$ . When held high, forces the part into a power down standby mode. The negative edge of Pwdn/Rst signal initiates a complete part (POR) reset. Ground for normal operation |

| 7                 | DINP                      | Positive Data Input                                                                                                                                                                                                                 |

| 8                 | DINN                      | Negative Data Input                                                                                                                                                                                                                 |

| 9                 | SPI_sel                   | Control input. When held high indicates SPI is selected (internally pulled down with $60 \text{K}\Omega$ ). When low I2C is selected                                                                                                |

| 10                | V <sub>CC</sub> _LD       | V <sub>CC</sub> for the laser driver section. Connect to V <sub>CC</sub>                                                                                                                                                            |

| 11                | TX_Fault                  | Safety circuit fault indicator. Open collector output, external resistor pull up to host_V <sub>CC</sub> required                                                                                                                   |

| 12                | TX_DIS                    | Control input for Transmit disable. When high or left floating, shuts off both bias and modulation outputs. Set low for normal operation. 7 k $\Omega$ internal resistor pull-up to $V_{CC}$                                        |

| 13                | GND                       | Ground. Must be connected to ground for proper device operation                                                                                                                                                                     |

| 14                | IPIN                      | Photodiode current monitor                                                                                                                                                                                                          |

| 15                | IBOUT <sub>CA</sub> /SGND | Bias current output for common anode operation. Internal ground switch for common cathode operation                                                                                                                                 |

| 16                | GND0                      | Ground for modulation output stage. Must be connected to ground for proper device operation                                                                                                                                         |

| 17                | CC <sub>sel</sub>         | When high, common cathode is selected. When low or floating, common anode is selected (internally pulled down with 60 k $\Omega$ )                                                                                                  |

| 18                | OUTP                      | Positive modulation output                                                                                                                                                                                                          |

| 19                | OUTN                      | Negative modulation output                                                                                                                                                                                                          |

| 20                | GPIO(4)/ BMON<br>DAC      | Analog General Purpose I/O. Input or Output or 6bit DAC (current sinking only)                                                                                                                                                      |

| 21                | SVCC/ IBOUT <sub>CC</sub> | Internal supply switch for common anode operation. Bias current output for common cathode operation                                                                                                                                 |

| 22                | A/D <sub>AUX2</sub>       | Auxiliary A/D input                                                                                                                                                                                                                 |

| 23                | BIAS_R                    | External resistor for precision bias reference                                                                                                                                                                                      |

| 24                | A/D <sub>AUX1</sub>       | Auxiliary A/D input                                                                                                                                                                                                                 |

Table 2-1. Pin Descriptions

| QFN Pin<br>Number | Name               | Function                                                                                                                                                                                                                                                                                |

|-------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25                | A/D <sub>RxP</sub> | A/D input for received power monitor                                                                                                                                                                                                                                                    |

| 26                | TEST               | Input for self test. When high, self test is initiated. Connect to ground for normal operation. (internally pulled down with $60~\text{k}\Omega)$                                                                                                                                       |

| 27                | RxLOS              | Can be selectable Input or Output. If used as input pin, it is Loss of signal from limiting amp (internally pulled down with 60 k $\Omega$ ). If used as output, it's an ope collector output                                                                                           |

| 28                | GPI0(3)/RS1        | For SFP+: Can be configured as RS1 rate select (internally pulled down with 60 kΩ using an internal switch) For non SFP+: General purpose I/O                                                                                                                                           |

| 29                | GPIO(2)/SS<br>/PWA | For SPI interface: Slave Select is input to M02171 (should be externally terminated with resistor required for application). Must be low before the data transaction and stay low for the duration of the transaction.  For non-SPI: General purpose I/O or 6bit DAC. Current sink only |

| 30                | GPIO(1)/           | For SPI interface: SPI_CK is the clock input (10MHz)                                                                                                                                                                                                                                    |

|                   | SPI_CK/6bit<br>DAC | For non SPI: General purpose I/O or 6 bit DAC (current sourcing or sinking)                                                                                                                                                                                                             |

| 31                | GPIO(0)/           | General purpose I/O or 10 bit DAC. Output can be current or voltage. In current mode, DAC output can only source                                                                                                                                                                        |

|                   | 10 bit DAC         | current                                                                                                                                                                                                                                                                                 |

| 32                | DVDD               | Internally regulated to 1.8V for Digital circuitry. Typically connect a 10nF capacitor to ground                                                                                                                                                                                        |

| Paddle            | GND                | Ground. Must be connected to ground for proper device operation                                                                                                                                                                                                                         |

#### Table 2-2. GPIO PIN Mapping

| QFN Pin<br>Number | Pin Name                   | Integrated Mode<br>SFP Function | External Micro mode<br>SFP Function | External Micro mode<br>XFP Function |

|-------------------|----------------------------|---------------------------------|-------------------------------------|-------------------------------------|

| 20                | GPIO(4)/ BMON_MAG DAC      | GPIO or DAC                     | GPIO or DAC                         | GPIO or DAC                         |

| 28                | GPIO(3)/ RS1               | RS1 or GPIO                     | RS1 or GPIO                         | GPI0                                |

| 29                | GPIO(2)/ SS /PWA DAC       | GPIO or DAC                     | GPIO or DAC                         | GPIO or DAC                         |

| 30                | GPIO(1)/ SPI_CK/ 6 bit DAC | GPIO or DAC                     | GPIO or SPI or DAC                  | GPIO or SPI or DAC                  |

| 31                | GPIO(0)/ 10 bit DAC        | GPIO or DAC                     | GPIO or DAC                         | GPIO or DAC                         |

M02171 8/10G VCSEL Driver + Micro Controller Pinout 32 31 30 26 25 AVDRXP RxLOS GPIO(2) /SSB /PWA GPIO(3) Test NVRAM1 SDA A/DAUX1 24 1 NVRAM2 SCL BIAS\_R 2 23 MOD-DEF1 /SPI\_O A/DAUX2 3 22 5mm X 5mm QFN SVCC //BOUTCC 21 package MOD-DEF2 /SPI\_I GPIO(4)/ Bmon\_Mag VCC 5 20 Ground Downbond to Center Paddle OUTN 19 Pwdn/Rst DINP OUTP 7 18 CCsel 17 8 DINN TX\_Fault TX\_DIS IBOUTCA / SGND GNDO SPI\_Sel GND M VccLD 9 10 11 12 13 14 15 16

Figure 2-1. Pin Assignments for M02171 Device

NOTE:

The package bottom must be adequately grounded to ensure correct thermal and electrical performance. Please reference the Amkor Application Note "Application Notes for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages" at www.amkor.com (http://www.amkor.com/products/notes\_papers/MLFAppNote.pdf).

# 3.0 Functional Description

#### 3.1 Overview

The M02171 provides a highly integrated SFF-8472 solution for fiber optic transceivers. It combines the Digital Diagnostic Monitoring Interface for SFF-8472 with a laser driver compatible with VCSELs.

The M02171 monitors temperature, voltage, bias and modulation current, transmit receive power, and other userdefined external parameters. Internal ADCs and comparators allow each parameter to be compared against userdefined threshold levels to provide indication of a fault condition. Integration of the laser driver provides digital control of the laser bias and modulation currents in addition to pulse width control of the modulation current.

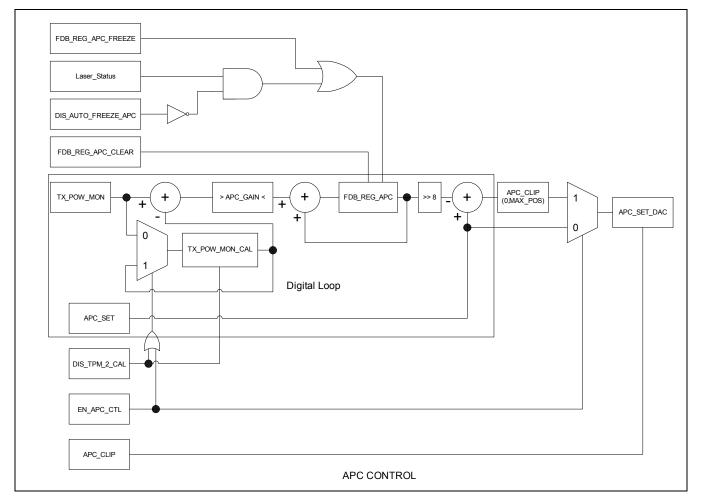

Integrated safety circuitry provides latched bias and modulation current shutdown if a fault condition is detected and provides an internal V<sub>CC</sub> switch for common anode operation and an internal ground switch for common cathode operation.

Microprocessor Laser Laser **GPIOs** Controller System Driver SRAM Program SFP DDMI User/ /Data Memory Memory Vendor Registers (2 port) Two-Wire **NVRAM** Interface Controller Controller External **EEPROM**

Figure 3-1. M02171 Architecture

# 3.2 Features

- Laser Driver with integrated digital diagnostic functions

- 155 Mb/s 11.3 Gb/s operation

- Integrated power supply switch for redundant shutdown

- Dual closed-loop OMA control, single-closed-loop and open-loop operation with independently programmable bias and modulation currents

- Compliant with SFF-8431, Rev 3.1 "SFP+" standard for 8.5 and 10.3Gbps

- Compliant with SFF-8472, Rev 10.3: Diagnostic Monitoring Interface for Optical Transceivers

- Temperature

- Bias current

- TX Optical Power

- RX Optical Power

- Supply voltage

- Software control of Rate Select, Tx Fault, Tx Disable and Rx LOS

- Alarm/Warning flags are implemented for monitored quantities

- Supports Internal test and calibration

- Automatic power control

- SFP/SFP+ compliant safety circuitry with user selectable bypass

- Pulse width adjustment compensates for asymmetrical laser rise and fall times

- Five user configurable General Purpose I/Os

- Up to four user configurable DAC outputs

- Two available auxiliary 12 bit ADC inputs

- SPI or 2-wire interface, compatible with Serial ID, as defined in the SFP MSA

- Internal A/D D/A loopback for real time diagnostics

- User and OEM password protection

- Power-on meter (journal timer)

- 12 bit ADC resolution results in exceptional monitor accuracies

- Compact: 32 pin QFN, 5mm x 5mm

- Operating Temp: -40 °C to +95 °C

# 3.3 General Description

#### 3.3.1 Overview

The M02171 integrates the digital diagnostic monitoring requirements of SFF-8472 with a highly integrated laser driver intended for applications to 11.3 Gbps. The level of integration allows easy set up and calibration of laser power and extinction ratio. The timing requirements of SFF-8472 and the SFP/SFP+ MSA are met when using the M02171 including soft control timing and status functions of both standards. In addition, integration allows the modulation current monitor to be available digitally and two auxiliary A/Ds are available for customer use in providing features beyond the standards requirements.

The M02171 provides a turn-key solution for SFF-8472 and SFP/SFP+ compliant modules by including firmware that provides the mandatory features of both and enables the manufacturer to easily implement any optional features of their choosing using a simple GUI interface. The M02171 enables automatic module calibration and test that allows for a significant reduction in test cost and complexity.

Many features are user-adjustable, including the APC loop bias control, modulation current including temperature compensation control of the modulation current and laser pulse width adjustment. The M02171 utilizes control of both the bias and modulation currents which allows for management of the optical extinction ratio by compensating for the effects of temperature and aging of the laser.

Safety circuitry is also included to provide a latched shut-down of laser bias and modulation current if a fault condition occurs. An internal  $V_{CC}$  switch provides redundant shutdown when operating the device. Safety logic behavior is user configurable.

#### 3.3.2 Digital Diagnostic Monitoring Interface Features

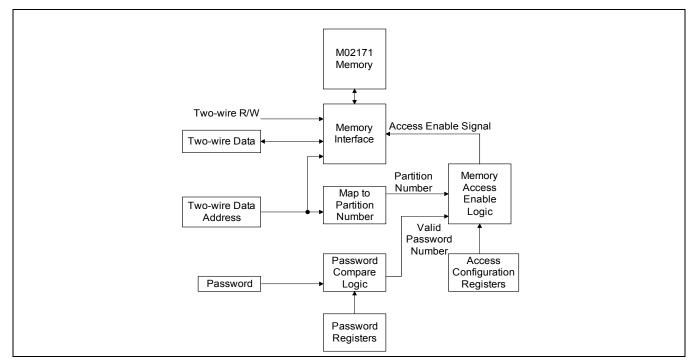

This section provides detail on how the Digital Diagnostic Monitoring Interface specified in SFF-8472 is supported in the M02171. The DDMI data is stored in an external EEPROM and accessed through the two-wire serial interface. EEPROM memory is also required to store SFP/SFP+ data, microprocessor code and initial device register values. In order to minimize the additional module complexity and expense of multiple external EEPROMs, the M02171 employs internal memory caches to store the SFP and DDMI data on-chip.

There are two serial interfaces. One (pins MODDEF2\_SDA and MODDEF1\_SCL) provides access by the host to the stored data. The other (pins NVRAM1\_SDA and NVRAM2\_SCL) is the interface to the single external EEPROM. Upon power-up, when the device comes out of reset, the device register values are downloaded, followed by the SFP and DDMI data and finally, the microprocessor program code is downloaded and the microprocessor enabled. The timing requirements are given in the Product Specifications Section 1.5, "Soft Control Timing Management," on page 8.

Two time-stamped versions of the DDMI data are stored in the EEPROM (DDMI 0 and DDMI 1, see Figure 4-4) to ensure that at least one valid data set is available in the event that a module failure occurred when the M02171 was in process of writing data from the on-chip cache memory to the external EEPROM. Each data set (DDMI 0 and DDMI 1) has a checksum for the purpose of determining data integrity. The most recent valid data set is copied to the cache. The SFP data and the microprocessor program code each have their own checksum to determine their integrity similar to the DDMI data.

While the module is in an active state, the data in the DDMI cache is updated by the microprocessor at intervals in compliance with the timing requirements of SFF-8472. The host also has access through the serial interface. To comply with the data integrity requirement, the microprocessor first checks to determine if the host is accessing data before updating the memory. In that event, the update is delayed until the activity ceases. Before the update occurs, the microprocessor also disables the acknowledgement signal of the two-wire interface to prevent the host from initiating a memory access while the cache is being updated.

#### 3.3.2.1 DDMI Real-Time Diagnostic Monitoring

Each monitor is independently enabled (to conserve power) by programming the corresponding bit of the ADC\_EN register to a 1. The M02171 DDMI memory is updated by the internal M02171 controller with an update interval of < 100 ms (typically 30 ms). The internal M02171 controller must supply the appropriate password before it is allowed to update the DDMI information to prevent corruption of the data if the controller arrives at an unstable state.

The "Ack" of the two-wire interface is disabled during DDMI update. To minimize the duration of the interruption of host access, the internal M02171 controller writes the updated information to shadow registers which is then burst-loaded into the DDMI memory. The interruption of host access will be  $< 1.2 \mu s$ .

The DDMI information is periodically copied back to the external EEPROM for protection against loss due to events such as power outages. The frequency of backup is once every twelve hours (derived from the journal timer). Backup of serial ID, diagnostic and other on-chip memory can be initiated by the host through the two-wire interface.

Having separate on-chip and external nonvolatile storage of the DDMI data is a distinct advantage of the M02171 because it allows rapid update of the DDMI data available to the host without exhausting the write endurance of the EEPROM in a short time period. The two most recent backups of the DDMI data are maintained in the external EEPROM at all times. This ensures that a valid data set remains if there is a module failure during the backup operation. Each version has a checksum and a time stamp which determines the most current version. If the information must be reloaded to the on-chip memory, the most recent version with a valid checksum is copied from the EEPROM. The backup operation is transparent to the host with no access interruption.

#### 3.3.3 Calibration

The M02171 supports both internal and external calibration as defined by SFF-8472. For internal calibration, the calibration is performed by the M02171 internal controller under software control. For external calibration, the controller simply writes the ADC values to the DDMI memory. One of the two calibrations modes must be enabled to achieve the accuracy specifications.

#### 3.3.4 Alarm and Warning Thresholds

The M02171 supports all the alarm and warning indications defined in SFF-8472. Each A/D quantity has a corresponding high alarm, low alarm, high warning and low warning threshold. These values are defined by the module manufacturer during module initialization and/or calibration and allow the module user to determine when a particular value is outside of "normal" limits as determined by the module manufacturer. For these indications to be active the thresholds defined in Table 3.15 of SFF-8472 Rev 10.3 "Alarm and Warning Thresholds (2-Wire Address A2h)" must be set. The nominal response time from an alarm or warning condition to the update of the corresponding status bit is 100 msec.

The M02171 provides very accurate indication of the present conditions of the module. The sampled diagnostic monitoring signals are stored in device registers. The comparison of each to the corresponding stored threshold values is performed under program control of the microprocessor. Using firmware it is possible to compensate the alarm and warning indications for temperature variations.

### 3.3.5 Optional Status and Control Bits

The M02171 supports all optional status and control bits (byte 110 of 2 Wire address A2h)defined in Table 3.17 of SFF-8472 Rev 10.3.

# 3.3.6 Data Inputs

The inputs to the internal data buffer are self-biased through resistors to an internal reference voltage  $V_{TT}$ . Input signals can be AC coupled to the part by allowing  $V_{TT}$  to float, which sets the common mode input voltage to approximately  $V_{CC}$  - 1.3V. Both CML and PECL input signals can be AC coupled to the M02171.

# 3.3.7 Equalization

For SFP+ applications, the input data can be equalized by enabling the equalizer. SFP+ specifies the jitter requirements at the input of the transmitter under various host board transmission line lengths for both microstrip and stripline. Table 3-1 shows common host board configurations with maximum recommended SFP+ host board trace lengths.

| Table 0-1. Tiogi board i Ob maximum nace ichiquis | Table 3-1. | Host board PCB maximum trace lengths |

|---------------------------------------------------|------------|--------------------------------------|

|---------------------------------------------------|------------|--------------------------------------|

| Туре       | Material                | Trace Width (mm) | Loss Tan | Trace Length (mm) |

|------------|-------------------------|------------------|----------|-------------------|

| Microstrip | Standard FR4 (4000-6/8) | 0.3              | 0.022    | 200               |

|            | Nelco (4000-13)         | 0.3              | 0.016    | 300               |

| Stripline  | Standard FR4 (4000-6/8) | 0.125            | 0.022    | 150               |

|            | Nelco (4000-13)         | 0.125            | 0.016    | 200               |

#### 3.3.8 Data Polarity / Pulse Width Adjust

After the data passes through the data input buffer, it enters the pulse width adjust buffer. It incorporates a polarity selection as well as a pulse width adjustment control to compensate for laser pulse width distortion. By adjusting the current from the PWA DAC, pulse width can be adjusted from 20% to 80%. Pulse width control can be disabled by setting the PWA\_EN bit low, resulting in approximately 50% crossing point at the output and reduces the supply current by 2mA.

#### 3.3.9 Output Buffer

After the data passes through the pulse width adjust buffer, it enters the output buffer. The output buffer reshapes and ground reference the signal in order to drive the output stage with enough speed and correct output levels.

### 3.3.10 Photodiode polarity

M02171 supports common anode or common cathode photodiode independently from the laser mode.

#### 3.3.11 Rate select function

To comply with the SFP+ rate select requirement, when the device in low rate mode, power is reduced in the signal path and the compensation is switched on at the outputs.

#### 3.3.12 **Pwdn/Rst**

This is a multifunction input pin for module power down and reset. When held "high", in order to meet the power dissipation requirements of XFP applications, the laser is forced to low rate mode and the modulation and bias currents are not set by the DAC. They are set by an internal current reference of low value in order to reduce the power dissipation of the module.

# 3.3.13 Laser Driver Output Stage

The output stage incorporates feedback to maintain performance over the range of laser modulation current. The output stage is nominally configured to be AC coupled to VCSEL's with resistances from 40 - 100 $\Omega$ . The M02171 has internal 50 $\Omega$  terminations between the outputs (OUTP and OUTN) and the internal supply.

The laser driver output stage is separately grounded from the rest of the circuitry (through GNDO) for optimum performance and control of output characteristics.

Two independent high-frequency compensation networks are included to allow additional flexibility with setting the output response characteristics. A binary network and an additional three bits (OC0, OC1, OC2) can be used to

tune two separate internal RC networks at the M02171 output providing control of output stage damping in order to optimize the optical eye diagram.

Laser modulation current is controlled by adjusting the MODSET DAC current. The modulation current can be temperature compensated in the digital state machine by changing the MODSET DAC current by a programmed ratio to the temperature ADC reading. Refer to Section 3.3.16, "Modulation Current Control," on page 27.

When Pwdn/Rst is high, the MODSET DAC is disconnected and the modulation is set below its lowest value.

#### 3.3.14 GPIO Operation

The M02171 has five GPIOs that can individually be configured as a digital input, a digital input with an interrupt, a digital output, or the output of a DAC. When configured as a digital input the device firmware responds to the signal level on the GPIO. The rate of polling of the GPIO configured as a digital input is defined within the firmware which if implemented, would typically result in polling intervals of 20 ms. The digital input with an interrupt is used in the same way, but as an interrupt the response time to a signal change is typically 3 ms. The interrupt method is completely configurable as one of the four following formats: low level or high level causes the interrupt, or rising or falling edge causes the interrupt. As a digital output, the level can be fixed during device initialization/calibration or can be varied by the device firmware (i.e. as a rate select output to a limit amp responding to the module rate select input). Finally, each GPIO can be the output of one of the internal DACs. The DAC mapping is shown in the block diagram and similar to a digital output, the level can be fixed during device initialization/calibration or can be varied by the device firmware changing the DAC setting in response to a defined event.

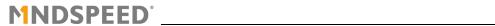

#### 3.3.15 Automatic Power Control

The M02171 incorporates unique and innovative options for controlling the transmitted laser power. Control mechanisms are provided for controlling both the bias current and the modulation current. Each includes multiple techniques which can be independently enabled or disabled. This allows maximum configurability in a wide variety of applications and choice of laser.

#### 3.3.15.1 Bias Current Control

The M02171 allows two methods of controlling the laser bias current: closed loop digital control and open loop control. Each mode is enabled by selections made within the device register settings.

Control of the bias current is illustrated in Figure 3-3. TxPwrMon is an internally mirrored replica of the current flowing into IPIN. The updated TxPwrMon value is written to the TX\_POW\_MON registers. All modes start with setting the target output power by writing to the APC\_SET registers.

Figure 3-2. Bias Current Control

#### 3.3.15.1.1 Closed loop Digital Control

M02171 includes circuitry to automatically maintain laser average output power with use of a monitor photodiode. Figure 3-3 shows various photo diode connection and PD polarity swap configuration examples.

Closed loop digital control is configured by setting EN\_APC\_CTL high. In closed loop digital control mode the APC\_SET registers are the uncalibrated reference level for the average optical power. Closed loop digital control varies the bias current (using the APC\_SET\_DAC value) to maintain the measured TX\_POW\_MON equal to the value stored in the TX\_POW\_MON\_CAL registers during module calibration.

Closed loop digital control is a state machine that utilizes the laser monitor photodiode and requires the desired average value of the output optical power to be stored in the TX\_POW\_MON\_CAL registers. An internal current mirror mirrors the monitor photodiode current at IPIN and is labelled TxPwrMON. The most recent value of TxPwrMon is stored in the TX\_POW\_MON register. The M02171 utilizes a precision integrator (low pass filter) on TX\_POW\_MON. The output of the integrator is compared to the desired average value of optical power in the TX\_POW\_MON\_CAL registers and the resulting 12 bits adjusts the bias current up or down accordingly through the APC\_SET\_DAC registers.

Common Anode; CC<sub>SEL</sub>=0 Common Cathode; CC<sub>SEL</sub>=1 IB<sub>OUT\_CC</sub> PD\_polarity\_swap = 0: IB<sub>OUT\_CA</sub> IPIN Monitor photodiode Monitor photodiode sinks current from IPIN sources current into IPIN IPIN IB<sub>OUT\_CC</sub> PD polarity swap = 1: IB<sub>OUT\_CA</sub> IPIN Monitor photodiode Monitor photodiode sources current into IPIN sinks current from IPIN

Figure 3-3. PD polarity swap configuration examples

#### 3.3.15.1.2 Open loop Control

With open loop control there is no feedback from the laser output to the bias control. A value is simply written that corresponds to the desired value of the output bias current. The bias current maintains this output level regardless of laser performance unless a fault condition occurs whereby the safety loop disables the bias current output.

Open loop control of the bias current is achieved by setting EN\_APC\_CTL low and writing the desired value of the APC\_SET DAC input to the APC\_SET register.

Even though the bias current is operating open loop, it is possible to implement temperature compensation under firmware control by using either a look-up table or a polynomial to modify the value with temperature.

#### 3.3.16 Modulation Current Control

Control of the modulation current is open loop with programmable compensation for changes in the bias current and for changes in the temperature. This is illustrated in Figure 3-4.

MOD\_CLIP >> BA\_COMP\_GAIN BIAS\_MON CLIP MODULATION **CURRENT** n 0 CONTROL BIAS\_MON\_CAL 1 MOD\_SET 0 DIS BM 2 CAL MOD\_SET\_DAC MOD\_CLIP **BIAS COMPENSATION** EN\_BIAS\_COMP TEMP\_START TEMP\_COEF1>> 0 INT TEMP MON 0 EXT\_TEMP\_MON 1 TEMP\_SEL X ≥ 0 EN\_TEMP\_COMP uP TEMP COMP TEMPERATURE COMPENSATION uP\_TEMP\_EN

Figure 3-4. Modulation Current Control

The target modulation current is set by writing to the MOD SET register.

#### 3.3.16.1 BIAS-Adjusted Compensation of Modulation Current

This form of compensation is configured by setting EN\_BIAS\_COMP high and EN\_TEMP\_COMP low. The BIAS\_MON ADC is periodically sampled. The new MOD\_SET\_DAC value is computed based on a ratio set in the BA\_COMP\_GAIN register.

The register BA\_COMP\_GAIN is equivalent to "percent bias current slope" factor adjustment on the modulation current. If BIAS\_MON (the present bias monitor output) is larger than the BIAS\_MON\_CAL value (established