# **Application Manual**

# Real Time Clock Module AB-RTCMK-32.768kHz Series ( I<sup>2</sup>C Interface )

### **Contents**

| 1.Overview                                                      | 3  |

|-----------------------------------------------------------------|----|

| 2.Block Diagram                                                 | 3  |

| 3.Outline drawing                                               | 4  |

| 4.Pin Functions                                                 | 4  |

| 5. Absolute Maximum Ratings                                     | 5  |

| 6.Recommended Operating Conditions                              | 5  |

| 7.Frequency Characteristics                                     | 5  |

| 8. Electrical Characteristics                                   |    |

| 8-1.DC Characteristics                                          | 6  |

| 8-2.AC Characteristics 1(I <sup>2</sup> C BUS Serial Interface) | 7  |

| 8-3.Timing Chart                                                | 7  |

| 8-4.AC Characteristics 2(CLKOUT)                                | 8  |

| 8-5.Power Supply Rise Time and Fall Time                        | 8  |

| 9.Method of Application                                         |    |

| 9-1.Time Control Register Table                                 | 9  |

| 9-2.Register Description                                        |    |

| 9-2-1. Time and Calendar Register (Address 00h to 06h)          | 10 |

| 9-2-2.Alarm Registers (Address 07h to 09h)                      | 11 |

| 9-2-3.Timer Counter Register (Address 0Ah)                      | 11 |

| 9-2-4.Select Registers (Address 0Bh)                            | 12 |

| 9-2-5.Flag Registers (Address 0Ch)                              | 13 |

| 9-2-6.Control Registers (Address 0Dh)                           | 14 |

| 9-3.Interrupt Function Description                              |    |

| 9-3-1.Fixed Cycle Timer Interrupt                               | 15 |

| 9-3-2.Alarm Interrupt                                           | 17 |

| 9-3-3. Time Update Interrupt                                    | 18 |

| 9-3-4.Interrupt Signal Identification                           | 19 |

| 9-4.I <sup>2</sup> C-BUS Serial Interface                       |    |

| 9-4-1.System Configuration                                      | 19 |

| 9-4-2.START Condition and STOP Condition                        | 20 |

| 9-4-3.Acknowledge Signal (ACK Signal)                           | 20 |

| 9-4-4.Slave Address                                             | 21 |

| 9-5.I <sup>2</sup> C-BUS Date Transfer Sequence                 |    |

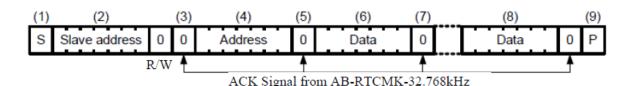

| 9-5-1.Data Writing Sequence                                     | 21 |

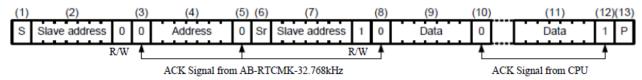

| 9-5-2.Data Reading Sequence                                     | 22 |

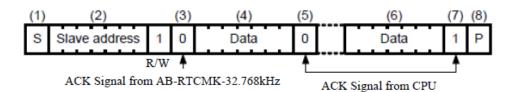

| 9-5-3.Data Reading Sequence when Address is not Specification   | 22 |

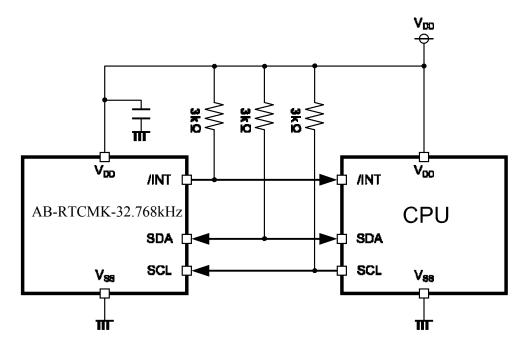

| 10.Connection with Typical Microcontroller                      | 23 |

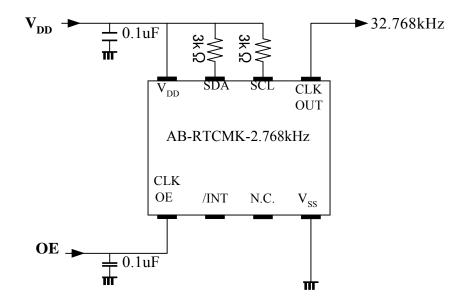

| 11.32kHz TCXO Circuit                                           | 23 |

| 12.Cautions                                                     |    |

| 13. Notes                                                       |    |

| 14 Terms and Conditions                                         | 25 |

# SMALL CERAMIC PACKAGE I<sup>2</sup>C-BUS Interface Real-time Clock Module

### AB-RTCMK-32.768kHz

- Frequency accuracy: +/-5.0ppm (-40deg.C to +85deg.C)

- Temperature compensating operation power supply voltage: 2.0V to 5.5V

- Time keeping Voltage: 1.3V to 5.5V

- I<sup>2</sup>C-BUS Serial Interface Voltage: 1.5V to 5.5V

- Low consumption current: Typ.0.6μA

- (VDD=3V, Temperature compensating interval30s, Clock output un-operating)

- I<sup>2</sup>C-BUS Serial Interface: 400 kHz Fast mode correspondence

- Clock function: Hour/ Min / Sec

- The leap year automatic distinction calendar function by 2099

- Alarm interruption function for day, date, hour and minute settings

- A constant cycle timer interruption function: 244.14us to 255 min

- Time update interruption function: Min / Sec

- Clock output function: 32.768kHz / 1024Hz / 32Hz / 1Hz

- Power supply voltage detection function: 2.0V temperature compensated voltage detection

1.5V Low power supply voltage detection

## 1. Overview

This module is a real time clock module of the I2C-BUS interface system which built in 32.768kHz DTCXO. In addition to the clock and the calendar function, it has an alarm interruption function, the constant cycle timer interruption function, the time update interruption function, the clock output function, and the power supply voltage detection function.

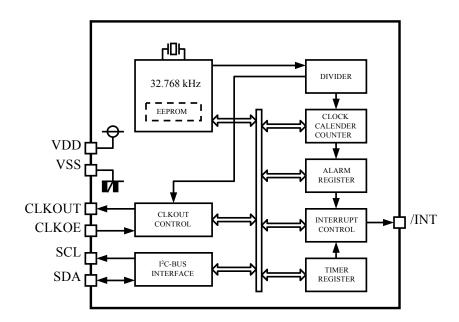

# 2. Block Diagram

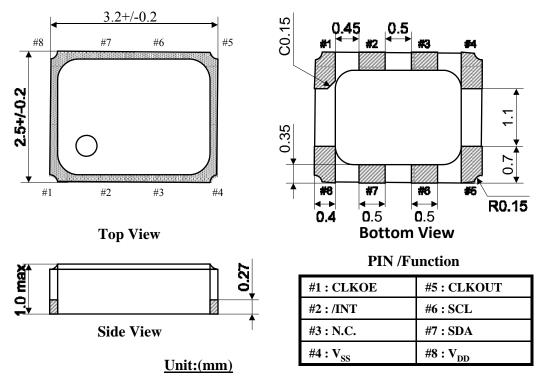

# 3. Outline Drawing

\*N.C. connected to VSS inside.

# 4. Pin Functions

| Pin Name          | I/O | Function                                                                                                                                                                                        |

|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |     | This is an input pin used to control the output mode of the CLKOUT pin.                                                                                                                         |

| CLKOE             | I   | When this pin's level is high, the CLKOUT pin is in output mode.                                                                                                                                |

|                   |     | When it is low, the CLKOUT pin is ''Hi-Z" (High Impedance).                                                                                                                                     |

| /INT              | О   | This pin is used to output alarm signals, timer signals, timer update signals, and other signals. This pin is an open drain pin.                                                                |

| $V_{SS}$          |     | This pin is connected to a ground                                                                                                                                                               |

|                   |     | This pin outputs a 32.768kHz signal.                                                                                                                                                            |

| CLKOUT            | О   | This is the CMOS output pin with output control provided via the CLKOE pin.                                                                                                                     |

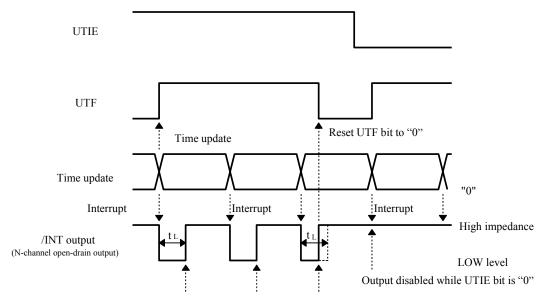

| SCL               | I   | This is the serial clock input for I2C BUS communications.                                                                                                                                      |

|                   |     | This is the serial data input/output for I2C BUS communications.                                                                                                                                |

| SDA               | I/O | This pin's signal is used for input and output of address, data, and ACK bits, synchronized with the serial clock used for I2C communication. This pin is an N-ch open drain pin during output. |

| $V_{\mathrm{DD}}$ | _   | This pin is connected to a positive power supply.                                                                                                                                               |

# 5. Absolute Maximum Rating

| Parameter                    | Symbol            | Conditions    | Rating                       | Unit  |

|------------------------------|-------------------|---------------|------------------------------|-------|

| Power supply voltage(*1)     | $V_{\mathrm{DD}}$ |               | -0.3 to +6.5                 | V     |

| Input voltage(*1)            | $V_{IN}$          | SCL,SDA,CLKOE | -0.3 to +6.5                 | V     |

| Output voltage1(*1)(*2)      | $V_{OUT1}$        | CLKOUT        | -0.3 to V <sub>DD</sub> +0.3 | V     |

| Output voltage2(*1)          | $V_{OUT2}$        | SDA,/INT      | -0.3 to +6.5                 | V     |

| Preservation temperature(*3) | $T_{STG}$         |               | -55 to +125                  | deg.C |

<sup>\*1:</sup> It is a value which must not exceed even a moment.

If it should exceed, there is concern of destruction of IC, characteristic degradation, and a reliability fall

# 6. Recommendation Operation Conditions

| Parameter                                 | Symbol            | Conditions         | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------|--------------------|-----|-----|-----|------|

| Power supply voltage                      | $V_{\mathrm{DD}}$ | Ta=-40 to +85deg.C | 1.3 | 3.0 | 5.5 | V    |

| Time keeping voltage                      | $V_{ m DDT}$      | Ta=-40 to +85deg.C | 1.3 | 3.0 | 5.5 | V    |

| Interface operation voltage               | $V_{int}$         | Ta=-40 to +85deg.C | 1.5 | 3.0 | 5.5 | V    |

| Temperature compensated operation voltage | $V_{TEM}$         | Ta=-40 to +85deg.C | 2.0 | 3.0 | 5.5 | V    |

<sup>\*</sup> Since reliability may be affected if it is used out of the recommendation operation condition range, please use it within the limits of this.

# 7. Frequency Characteristic

| Parameter                 | Item | Conditions                              | spec      | Unit |

|---------------------------|------|-----------------------------------------|-----------|------|

| Frequency accuracy        | df/f | Ta=-40 to 85deg.C,V <sub>DD</sub> =3.0V | +/-5.0*   | ppm  |

| Oscillation time of onset | Tsta | Ta=25deg.C,V <sub>DD</sub> =3.0V        | 1.0(max.) | sec  |

<sup>\*</sup> Monthly difference 13 seconds

<sup>\*2:</sup> It is a value which VDD value is a VDD value of recommendation operation power supply voltage.

<sup>\*3:</sup> It is a case of N2 or the simple substance preservation by a vacuum atmosphere.

<sup>\*</sup> About the details of frequency accuracy, I correspond at the time of an individual specification exchange.

# **Electrical Characteristics**

### **DC** Characteristics **8.1.**

$V_{SS}$ =0V,  $V_{DD}$ =3.0V, Ta=-40 to 85deg.C

| Parameter                   | Symbol              | Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | onditions                                              |                        | MIN | TYP | MAX                 | Unit |

|-----------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|-----|-----|---------------------|------|

|                             | $I_{DD1}$           | SCL=SDA=/INT= V <sub>D</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        | $V_{DD} = 5 \text{ V}$ |     | 1.0 | 4.0                 |      |

|                             | $I_{\mathrm{DD2}}$  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CLKOUT Non-operating output Compensation interval 30 s |                        |     | 0.6 | 2.0                 | μА   |

|                             | $I_{\mathrm{DD3}}$  | SCL=SDA=/INT=V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | o, CLKOE= V <sub>DD</sub>                              | $V_{DD} = 5 \text{ V}$ |     | 2.5 | 7.0                 |      |

| Current consumption         | $ m I_{DD4}$        | CLKOUT output 32.76<br>pF(*1)output at no load<br>Compensation interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $V_{DD} = 3 \text{ V}$                                 |                        | 1.5 | 4.0 | μΑ                  |      |

|                             | $I_{\mathrm{DD5}}$  | SCL=SDA=/INT= V <sub>D</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{\rm DD} = 5 \text{ V}$                             |                        | 350 | 700 |                     |      |

|                             | $I_{\mathrm{DD6}}$  | CLKOUT Non-operation Clear Compensation Compensation Compensation Compensation Clear Clear Compensation Clear Clea | -                                                      | 150                    | 300 | μΑ  |                     |      |

| High level input voltage    | $V_{IH1}$           | SCL, SDA, CLKOE pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $0.8~\mathrm{V_{DD}}$                                  |                        | 5.5 | V   |                     |      |

| Low level input voltage     | $V_{\rm IL1}$       | SCL, SDA, CLKOE pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SCL, SDA, CLKOE pins                                   |                        |     |     | $0.2 \times V_{DD}$ | V    |

| High level input voltage    | $V_{\mathrm{OH1}}$  | CLKOUT pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_{DD} = 5 \text{ V}, I_{OH}$                         | <sub>H1</sub> = -1 mA  | 4.5 |     | 5.0                 | V    |

| riigii ievei iliput voitage | $V_{\mathrm{OH2}}$  | CLKOUT pills                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{DD} = 3 \text{ V}, I_{OH}$                         | $_{H2}$ = -1 mA        | 2.2 |     | 3.0                 | V    |

|                             | $V_{OL1}$           | CLKOUT pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_{DD} = 5 \text{ V}, I_{OI}$                         | $_{1}=1 \text{ mA}$    | 0.0 |     | 0.5                 | V    |

|                             | $V_{OL2}$           | CLKOO1 pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_{DD} = 3 \text{ V}, I_{OI}$                         | _2= 1 mA               | 0.0 |     | 0.8                 | v    |

| Low level input voltage     | $V_{OL3}$           | /INT pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{DD} = 5 \text{ V}, I_{OI}$                         | $_{.3}$ = 1 mA         | 0.0 |     | 0.25                | V    |

|                             | $V_{OL4}$           | /IIVI pilis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_{DD} = 3 \text{ V}, I_{OI}$                         | <sub>4</sub> = 1 mA    | 0.0 |     | 0.4                 | v    |

|                             | $V_{OL5}$           | SDA pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $V_{DD} \ge 2 \text{ V}, I_{OL}$                       | $_{.5}$ = 3 mA         | 0.0 |     | 0.4                 | V    |

| Input leak current          | $I_{LK}$            | CLKOE, SCL, SDA pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $V_{SS}$                                               | -0.5                   |     | 0.5 | μΑ                  |      |

| Output leak current         | $I_{OZ}$            | CLKOUT, /INT, SDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -0.5                                                   |                        | 0.5 | μΑ  |                     |      |

| Power supply voltage        | $V_{ m DET1}$       | Temperature compensate detection (*2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Temperature compensating operation voltage             |                        |     | 1.9 | 2.0                 | V    |

| Detection voltage           | $V_{\mathrm{DET2}}$ | Low power supply vol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tage detection                                         |                        | 1.3 | 1.4 | 1.5                 | V    |

<sup>\*1:</sup> CLOUT is the IC external load capacitance connected to CLKOUT.

<sup>\*2:</sup> When VDD falls below VDET1, the internal detection circuit operates, and the intermittent temperature sensor output A/D converter stops. At the same time, the current data value in the CL[10-0] oscillator capacitance switching bits is retained. When VDD rises above VDETI again, the intermittent temperature sensor A/D converter is enabled.

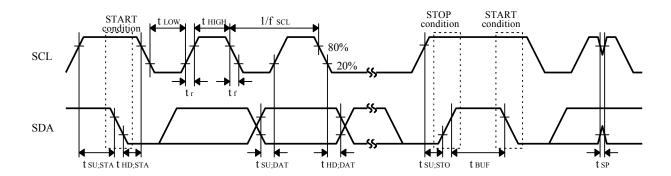

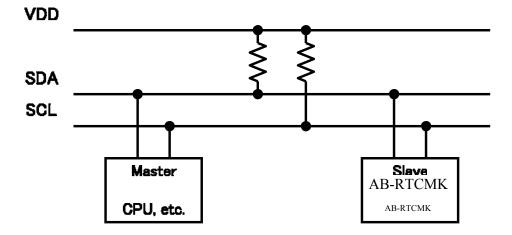

# 8.2. AC Characteristics

| Parameter                                       | Symbol              | Conditions          | MIN | TYP | MAX | Unit |

|-------------------------------------------------|---------------------|---------------------|-----|-----|-----|------|

| SCL clock frequency                             | $f_{SCL}$           |                     |     |     | 400 | kHz  |

| Start condition setup time                      | t <sub>SU;STA</sub> |                     | 0.6 |     |     | S    |

| Start condition hold time                       | t <sub>HD;STA</sub> |                     | 0.6 |     |     | S    |

| Data setup time                                 | t <sub>SU;DAT</sub> |                     | 100 |     |     | ns   |

| Data hold time                                  | t <sub>HD;DAT</sub> |                     | 0   |     | 900 | ns   |

| Stop condition setup time                       | t <sub>SU;STO</sub> |                     | 0.6 |     |     | S    |

| Bus free time between start and stop conditions | t <sub>BUF</sub>    |                     | 1.3 |     |     | S    |

| SCL "L" pulse width                             | $t_{LOW}$           |                     | 1.3 |     |     | S    |

| SCL "H" pulse width                             | $t_{ m HIGH}$       |                     | 0.6 |     |     | S    |

| SCL,SDA rise time                               | t <sub>r</sub>      | 20%→80%             |     |     | 0.3 | S    |

| SCL,SDA fall time                               | $t_{\mathrm{f}}$    | 80%→20%             |     |     | 0.3 | S    |

| Maximum bus spike time                          | $t_{SP}$            |                     |     |     | 50  | ns   |

| Due line lead conseitance                       | C                   | $V_{DD} \ge 1.8V$   |     |     | 400 | ъE   |

| Bus line load capacitance                       | $C_b$               | $V_{DD} \cdot 1.8V$ |     |     | 50  | pF   |

<sup>\*</sup>WF8592A access from the transfer of the start condition until the stop condition should be completed within 0.5 seconds. If the access exceeds 0.5 seconds, an internal monitor timer forcibly terminates the RTC bus interface access.

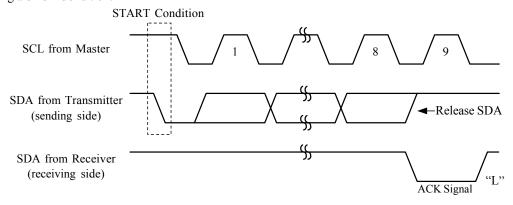

# 8.3. Timing Chart

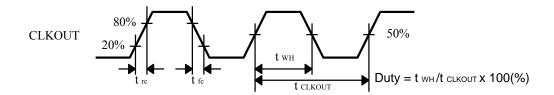

# 8.4. AC Characteristics

| Parameter                 | Symbol                                    | Co                                        | onditions                                 | MIN                          | TYP | MAX  | Unit |    |

|---------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|------------------------------|-----|------|------|----|

| CLKOUT duty               | Duty                                      | $C_{LOUT}$ =15pF, (                       | 40                                        | 50                           | 60  | %    |      |    |

|                           |                                           |                                           | V <sub>DD</sub> =1.8 to 5.5V              |                              | -   | 70   | ns   |    |

| CLKOUT rise time          | $t_{rC}$                                  | $C_{LOUT}$ =15pF<br>20% $\rightarrow$ 80% | $C_{LOUT}$ =15pF<br>20% $\rightarrow$ 80% | V <sub>DD</sub> =1.5 to 5.5V |     |      | 180  | ns |

|                           |                                           |                                           | V <sub>DD</sub> =1.5 to 5.5V              |                              |     | 1100 | ns   |    |

|                           |                                           |                                           | V <sub>DD</sub> =1.8 to 5.5V              |                              |     | 70   | ns   |    |

| CLKOUT fall time $t_{fC}$ | $C_{LOUT}$ =15pF<br>80% $\rightarrow$ 20% | V <sub>DD</sub> =1.5 to 5.5V              |                                           |                              | 180 | ns   |      |    |

|                           |                                           | 2070                                      | V <sub>DD</sub> =1.3 to 5.5V              |                              |     | 1100 | ns   |    |

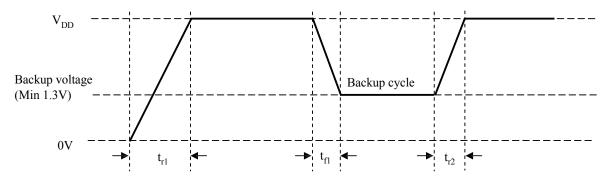

# 8.5. Power Supply Rise Time and Fall Time

| Parameter                                      | Symbol          | Conditions | MIN | TYP | MAX | Unit |

|------------------------------------------------|-----------------|------------|-----|-----|-----|------|

| Startup supply voltage rise time(*1)           | t <sub>r1</sub> |            | 10  |     | 10  | ms/V |

| Backup transition supply voltage fall time(*1) | t <sub>fl</sub> |            | 5   |     |     | us/V |

| Backup return supply voltage rise time(*1)     | T <sub>r2</sub> |            | 5   |     |     | us/V |

<sup>\*1:</sup> This device is equipped with a power-on reset circuit to initialize internal settings when power is first applied. If supply voltage rise time or fall time are outside the specified time, there is a possibility that the power on reset circuit may not be activated when power is first applied or during the backup transition/return cycle. Ensure supply voltage rise times and fall times are within the specified values for stable, correct, power-on reset circuit operation.

# 9. Method of Application

# 9.1. Time Control Register Table

| Address | Function            | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00h     | SEC                 | -     | S40   | S20   | S10   | S8    | S4    | S2    | S1    |

| 01h     | MIN                 | -     | M40   | M20   | M10   | M8    | M4    | M2    | M1    |

| 02h     | HOUR                | -     | -     | H20   | H10   | Н8    | H4    | Н2    | H1    |

| 03h     | WEEK                | -     | -     | -     | -     | -     | W4    | W2    | W1    |

| 04h     | DAY                 | -     | -     | D20   | D10   | D8    | D4    | D2    | D1    |

| 05h     | MONTH               | -     | -     | -     | MO10  | MO8   | MO4   | MO2   | MO1   |

| 06h     | YEAR                | Y80   | Y40   | Y20   | Y10   | Y8    | Y4    | Y2    | Y1    |

| 07h     | MIN Alarm           | AE    | MA40  | MA20  | MA10  | MA8   | MA4   | MA2   | MA1   |

| 08h     | HOUR Alarm          | AE    | RAM   | HA20  | HA10  | HA8   | HA4   | HA2   | HA1   |

| 001-    | WEEK Alarm          | AF    | WA6   | WA5   | WA4   | WA3   | WA2   | WA1   | WA0   |

| 09h     | DAY Alarm           | AE    | RAM   | DA20  | DA10  | DA8   | DA4   | DA2   | DA1   |

| 0Ah     | Timer Counter       | T128  | T64   | T32   | T16   | Т8    | T4    | T2    | T1    |

| 0Bh     | Select Register     | TCS1  | TCS0  | CFS1  | CFS0  | TSS1  | TSS0  | AS    | UTS   |

| 0Ch     | Flag Register       | -     | -     | VDHF  | VDLF  | -     | TF    | AF    | UTF   |

| 0Dh     | Control<br>Register | RESET | TEST  | RAM   | FIE   | TE    | TIE   | AIE   | UTIE  |

<sup>\*</sup> The register values are undefined when power is first applied; ensure the device is configured before use. Note that the TCS1, TCS0, CFS1, TEST, FIE, TE, TIR, AIE, and UTIE bits are reset to "0", and the VDLF bit is set to "1" when power is applied.

<sup>\*</sup> Bits indicated by a hyphen "-" are read-only bits with read output value of "0".

<sup>\*</sup> Only "0" data values can be written to the VDHF, VDLF, TF, AF, and UTF bits.

<sup>\*</sup> The TEST bit is a reserved bit for manufacturer testing, and should always be set to "0" for normal operation.

<sup>\*</sup> Since the write-in read-out operation to Address 0Eh and 0Fh causes malfunction, it is considered as an access inhibit.

# 9.2. Register Description

# 9.2.1. Time and Calendar Register (Address 00h to 06h)

| Address | Function | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|---------|----------|------|------|------|------|------|------|------|------|

| 00h     | SEC      | -    | S40  | S20  | S10  | S8   | S4   | S2   | S1   |

| 01h     | MIN      | -    | M40  | M20  | M10  | M8   | M4   | M2   | M1   |

| 02h     | HOUR     | -    | -    | H20  | H10  | Н8   | Н4   | Н2   | H1   |

| 03h     | WEEK     | -    | -    | -    | -    | -    | W4   | W2   | W1   |

| 04h     | DAY      | -    | -    | D20  | D10  | D8   | D4   | D2   | D1   |

| 05h     | MONTH    | -    | -    | -    | MO10 | MO8  | MO4  | MO2  | MO1  |

| 06h     | YEAR     | Y80  | Y40  | Y20  | Y10  | Y8   | Y4   | Y2   | Y1   |

### Data format

The time and calendar data is represented in BCD format.

### •HOUR register

The HOUR register contains the hour in 24-hour display mode.

### •WEEK register

The WEEK register increments using a 7-step up-counter(W4W2W1)=(000)—(001) —...  $\rightarrow$  (110)  $\rightarrow$  (000). The logic table for the (W4W2W1) bits for the day of the week are configurable by the user.

### •YEAR register

The YEAR register contains the last 2 digits of the western calendar year.

### •Automatic leap year correction function

The automatic leap year correction function corrects for leap years between 2000 and 2099.

### •Example time and calendar setting

For a time of 5:43:21 in the morning on Sunday, July 6, '98 (assuming the WEEK register setting for Sunday =(W4W2W1)=(000))

| Address   | Function  | bit 7 | bit 6 | bit 5 | bit 4   | bit 3 | bit 2 | bit 1 | bit 0 |

|-----------|-----------|-------|-------|-------|---------|-------|-------|-------|-------|

| Tradi ess | 1 unction | DIC 7 | 510 0 | 510 0 | , DIC . | DIC C | 510 2 | DIV 1 | 510   |

| 00h       | SEC       | _     | 0     | 1     | 0       | 0     | 0     | 0     | 1     |

| 01h       | MIN       | _     | 1     | 0     | 0       | 0     | 0     | 1     | 1     |

| 02h       | HOUR      | _     | _     | 0     | 0       | 0     | 1     | 0     | 1     |

| 03h       | WEEK      | -     | _     | _     | _       | -     | 0     | 0     | 0     |

| 04h       | DAY       | -     | _     | 0     | 0       | 0     | 1     | 1     | 0     |

| 05h       | MONTH     | _     | _     | _     | 0       | 0     | 1     | 1     | 1     |

| 06h       | YEAR      | 1     | 0     | 0     | 1       | 1     | 0     | 0     | 0     |

<sup>\*</sup>Time and calendar setting that are invalid will result in malfunction. Always ensure the data settings are valid.

# 9.2.2. Alarm Registers (Address 07h to 09h)

| Address | Function   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 07h     | MIN Alarm  | AE    | MA40  | MA20  | MA10  | MA8   | MA4   | MA2   | MA1   |

| 08h     | HOUR Alarm | AE    | RAM   | HA20  | HA10  | HA8   | HA4   | HA2   | HA1   |

| 001     | WEEK Alarm | A E   | WA6   | WA5   | WA4   | WA3   | WA2   | WA1   | WA0   |

| 09h     | DAY Alarm  | AE    | RAM   | DA20  | DA10  | DA8   | DA4   | DA2   | DA1   |

These registers specifies the alarm time using day of the week, day, hour, and minute settings. Address 09h specifies the day of the week or the day setting, selected by the AS (Alarm Select) bit in address 0Bh. The AF (Alarm Flag) bit in address 0Ch is set to "1" when a time is specified in the Alarm Registers.

• Assigning the day of the week using the WEEK Alarm register bits

The WEEK Alarm register WA0 to WA6 bits correspond to the bits in the WEEK register in address 03h:

(W4W2W1) = (000) to (110).

Example: When the WEEK register setting for Sunday = (W4W2W1) = (000)

| Address | Function   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 09h     | WEEK Alarm | AE    | Sat   | Fri   | Thu   | Wed   | Tue   | Mon   | Sun   |

The alarm can be set arbitrarily for multiple days of the week.

Example: Monday to Friday alarm, when the WEEK register setting for Sunday = (W4W2W1) = (000)

| Address | Function   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 09h     | WEEK Alarm | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 0     |

• Minute alarm, hourly alarm, daily alarm function

When the AE (Alarm Enable) bit 7 in a register is set to "1", the alarm is set to be triggered after every increment (minute, every hour, or every day) of the corresponding register.

Example: Alarm setting for 15 minutes past the hour for every hour

| Address | Function   | bit 7 | bit 7 bit 6                      |   | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|------------|-------|----------------------------------|---|-------|-------|-------|-------|-------|

| 07h     | MIN Alarm  | 0     | 0                                | 0 | 1     | 0     | 1     | 0     | 1     |

| 08h     | HOUR Alarm | 1     | Don't care bits when bit 7 = "1" |   |       |       |       |       |       |

<sup>•</sup> RAM bit

Can be used as a general-purpose RAM bit.

# 9.2.3. Timer Counter Register (Address 0Ah)

| Address | Function      | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0Ah     | Timer Counter | T128  | T64   | T32   | T16   | Т8    | T4    | T2    | T1    |

This register specifies the count value of a down-counter used for fixed-cycle timer interrupts.

The fixed-cycle timer source clock is specified using the TSS1 and TSS0 (Timer Source Clock Select) bits in address 0Bh.

When the TE (Timer Enable) bit in address 0Dh is changed from "0" to "1", the counter starts counting down from the specified count value. When the down-counter reaches zero, the TF (Timer Flag) bit in address 0Ch is set to "1".

The down-counter continually repeats counting down from the specified count value while the TE bit is set to "1".

# 9.2.4. Select Register (Address 0Bh)

| Address | Function        | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0Bh     | Select Register | TCS1  | TCS0  | CFS1  | CFS0  | TSS1  | TSS0  | AS    | UTS   |

• TCS (Temperature Compensation Select) bits

The TCS bits select the temperature compensation, operating interval.

Temperature compensation operates in sync with the clock register timing.

| TCS1 | TCS0 | Temperature compensation operating interval |

|------|------|---------------------------------------------|

| 0    | 0    | 0.5 sec                                     |

| 0    | 1    | 2 sec                                       |

| 1    | 0    | 10 sec                                      |

| 1    | 1    | 30 sec                                      |

<sup>\*</sup> When power is applied, TCS is reset to "00" and 0.5 sec temperature compensation operating interval is selected.

### • CFS (CLKOUT Frequency Select) bits

The CFS bits select the CLKOUT output frequency.

| CFS1 | CFS0 | CLKOUT output frequency |

|------|------|-------------------------|

| 0    | 0    | 32.768 kHz              |

| 0    | 1    | 1024 Hz                 |

| 1    | 0    | 32 Hz                   |

| 1    | 1    | 1 Hz                    |

<sup>\*</sup> When power is applied, CFS is reset to "00" and 32.768 kHz CLKOUT output frequency is selected.

### • TSS (Timer Source Clock Select) bit

The TSS bits select the fixed-cycle timer source clock.

| TSS1 | TSS0 | Timer source clock |

|------|------|--------------------|

| 0    | 0    | 4096 Hz            |

| 0    | 1    | 64 Hz              |

| 1    | 0    | 1 Hz               |

| 1    | 1    | 1/60 Hz            |

### • AS (Alarm Select) bit

The AS bit selects day of week alarm or day alarm.

The alarm data in address 09h is interpreted according to the following alarm setting.

| AS | Alarm type        |

|----|-------------------|

| 0  | Day of week alarm |

| 1  | Day alarm         |

### • UTS (Update Time Select) bit

The UTS bit selects the timing for generating time update interrupts.

| UTS | Time update interrupt timing |

|-----|------------------------------|

| 0   | Seconds digits update        |

| 1   | Minutes digits update        |

# 9.2.5. Flag Register (Address 0Ch)

| Address | Function      | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0Ch     | Flag Register | -     | -     | VDHF  | VDLF  | -     | TF    | AF    | UTF   |

### • VDHF (Voltage Detect High Flag) bit

The VDHF bit is the temperature compensation operating voltage detection flag.

Voltage detection is performed intermittently in sync with the temperature compensation operating interval timing.

| VDHF | Description                                                |

|------|------------------------------------------------------------|

| 0    | Supply voltage is V <sub>DET1</sub> (2.0 V max.) or higher |

| 1    | Supply voltage is V <sub>DET1</sub> (2.0 V max.) or lower  |

<sup>\*</sup> After detection, the VDHF bit is set to "1" and the value is maintained until you write "0". Only "0" data can be written to this bit.

### • VDLF (Voltage Detect Low Flag) bit

The VDLF bit is the supply voltage under-voltage detection and power-ON reset signal detection flag. Voltage detection is performed intermittently in sync with the temperature compensation operating interval timing.

| VDLF | Description                                                                                     |  |  |

|------|-------------------------------------------------------------------------------------------------|--|--|

| 0    | Supply voltage is $V_{\text{DET2}}$ (1.5 V max.) or higher, or power-ON reset signal undetected |  |  |

| 1    | Supply voltage is $V_{\text{DET2}}$ (1.5 V max.) or lower, or power-ON reset signal detected.   |  |  |

<sup>\*</sup> After detection, the VDLF bit is set to "1" and the value is maintained until you write "0". Only "0" data can be written to this bit.

### • TF (Timer Flag) bit

The TF bit is the fixed-cycle timer interrupt detection flag.

| TF | Description                            |  |

|----|----------------------------------------|--|

| 0  | Normal operation                       |  |

| 1  | Fixed-cycle down-counter zero detected |  |

<sup>\*</sup> After detection, the TF bit is set to "1" and the value is maintained until you write "0". Only "0" data can be written to this bit.

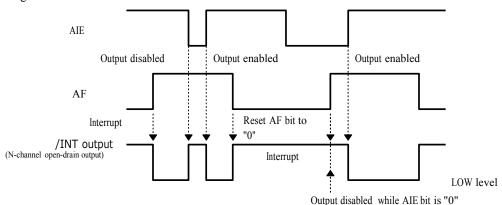

### • AF (Timer Flag) bit

The AF bit is the alarm interrupt detection flag.

| AF | Description         |  |

|----|---------------------|--|

| 0  | Normal operation    |  |

| 1  | Alarm time detected |  |

<sup>\*</sup> After detection, the AF bit is set to "1" and the value is maintained until you write "0". Only "0" data can be written to this bit.

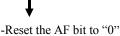

### • UTF (Update Time Flag) bit

The UTF bit is the time update interrupt detection flag.

| UTF | Description                     |

|-----|---------------------------------|

| 0   | Normal operation                |

| 1   | Time update completion detected |

<sup>\*</sup> After detection, the UTF bit is set to "1" and the value is maintained until you write "0". Only "0" data can be written to this bit.

# 9.2.6. Control Register (Address 0Dh)

| I | Address | Function         | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---|---------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 0Dh     | Control Register | RESET | TEST  | RAM   | FIE   | TE    | TIE   | AIE   | UTIE  |

### • RESET bit

| RESET | Description                                                       |  |

|-------|-------------------------------------------------------------------|--|

| 0     | Normal operation                                                  |  |

| 1     | 1 to 64 Hz frequency divider counter reset. Clock function stops. |  |

<sup>\*</sup> After setting the RESET bit to "1", this bit is reset to "0" after a STOP condition is received, after restart, or after a 0.5 sec I<sup>2</sup>C-bus interface reset.

### • TEST bit

The TEST bit is for manufacturer testing. Leave set to "0" for normal operation.

| TE | ST | Description           |

|----|----|-----------------------|

| C  | )  | Normal operating mode |

| 1  |    | Test mode             |

### • RAM bit

Can be used as a general-purpose RAM bit.

### • FIE (Frequency Interrupt Enable) bit

The FIE bit is the enable bit for the 50% duty, 1 Hz signal output on /INT.

| FIE | Description               |  |

|-----|---------------------------|--|

| 0   | /INT 1 kHz output disable |  |

| 1   | /INT 1 kHz output enable  |  |

<sup>\*</sup> When power is applied, FIE is reset to "0" and /INT output disable is selected.

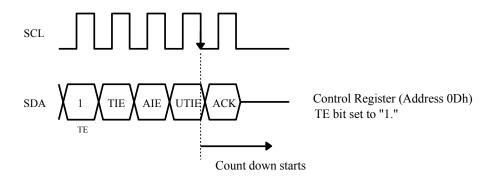

### • TE (Timer Enable) bit

The TE bit enables the fixed-cycle timer down-counter.

| TE | Counter operation |

|----|-------------------|

| 0  | Timer count stop  |

| 1  | Timer count start |

<sup>\*</sup> When power is applied, TE is reset to "0" and timer count stop is selected.

### • TIE, AIE, UTIE (Timer, Alarm, Update Time Interrupt Enable) bits

The TIE, AIE, and UTIE bits enable the interrupt signal outputs on /INT. TIE controls the fixed-cycle timer interrupt output, AIE controls the alarm interrupt output, and UTIE controls the time update interrupt output.

| TIE, AIE, UTIE | Description         |

|----------------|---------------------|

| 0              | /INT output disable |

| 1              | /INT output enable  |

<sup>\*</sup> When power is applied, these bits are reset to "0" and /INT output disable is selected.

The output from /INT is the logical-OR of the fixed-cycle timer interrupt, alarm interrupt, time update interrupt, and FIE-controlled 1 Hz signal outputs.

# 9.3. Interrupt Function Description

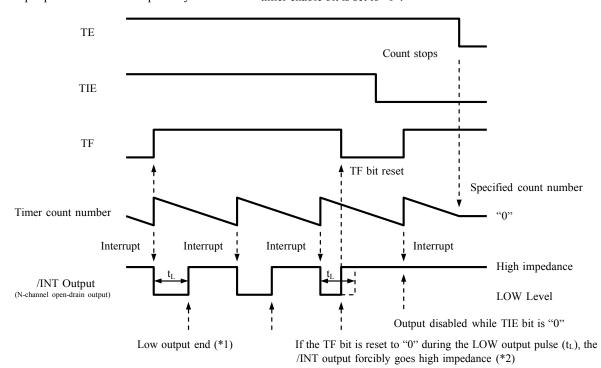

# **9.3.1.** Fixed Cycle Timer Interrupt