# SiS 746 AMD Athlon™/AMD Duron™ Clock Synthesizer

#### **Features**

- Supports AMD Athlon™/Duron™ CPU

- · 3.3V and 2.5V power supply

- · Eight copies of PCI clocks

- One 48-MHz USB clock

- · Two copies of ZCLK clocks

- One 48-MHz/24-MHz programmable SIO clock

- One differential CPU clock (opendrain)

- · One singled-ended CPU clock (opendrain)

- · SMBus support with readback capabilities

- Spread Spectrum electromagnetic interference (EMI) reduction

- · 48-pin SSOP package

| CPU | ZCLK | REF | PCI | AGP | IOAPIC | 48M | 24_48M |

|-----|------|-----|-----|-----|--------|-----|--------|

| x 2 | x 2  | x 3 | x 8 | x 2 | x 2    | x 1 | x 1    |

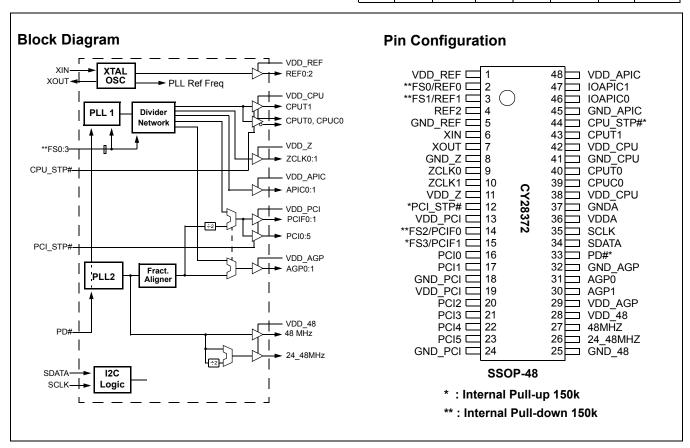

# **Pin Description**

| Pin #.                                               | Name                                                                                                          | Type | Description                                                                                                                                                                                     |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6                                                    | XIN                                                                                                           | I    | Crystal Connection or External Reference Frequency Input. This pin has dual functions. It can be used as an external 14.318-MHz crystal connection or as an external reference frequency input. |

| 7                                                    | XOUT                                                                                                          | 0    | <b>Crystal Connection</b> . Connection for an external 14.318-MHz crystal. If using an external reference, this pin must be left unconnected.                                                   |

| 4                                                    | REF2                                                                                                          | 0    | Reference Clock. 14.31818 reference outputs.                                                                                                                                                    |

| 2, 3                                                 | REF[0:1]/                                                                                                     | 0    | Reference Clock. 14.31818 reference outputs.                                                                                                                                                    |

|                                                      | FS[0:1]                                                                                                       | I    | Frequency Select. Sampled upon power-on to determine device operating frequency.                                                                                                                |

| 14, 15                                               | PCIF[0:1]/                                                                                                    | 0    | Free-running PCI. Independent of PCI_STP#.                                                                                                                                                      |

|                                                      | FS[2:3]                                                                                                       | I    | Frequency Select. Sampled upon power-on to determine device operating frequency.                                                                                                                |

| 16, 17, 20,<br>21, 22, 23                            | PCI [0:5]                                                                                                     | 0    | PCI Clock.                                                                                                                                                                                      |

| 12                                                   | PCI_STP#                                                                                                      | I    | PCI Stop. Stops all PCI clocks                                                                                                                                                                  |

| 40<br>39                                             | CPUT0<br>CPUC0                                                                                                | 0    | Differential CPU Outputs.                                                                                                                                                                       |

| 43                                                   | CPUT1                                                                                                         | 0    | "True" Clock of Differential CPU Outputs. For chipset host bus                                                                                                                                  |

| 44                                                   | CPU_STP#                                                                                                      | I    | CPU Stop. Stops all CPU clocks                                                                                                                                                                  |

| 9, 10                                                | ZCLK[0:1]                                                                                                     | 0    | MuTIOL Clock Outputs.                                                                                                                                                                           |

| 46, 47                                               | IOAPIC[0:1]                                                                                                   | 0    | IOAPIC. 2.5 V clock outputs                                                                                                                                                                     |

| 27                                                   | 48MHz                                                                                                         | 0    | 48-MHz Clock. USB clock outputs                                                                                                                                                                 |

| 26                                                   | 24_48MHz                                                                                                      | 0    | <b>24-MHz or 48-MHz Clock</b> . Selectable SIO clock outputs. Default output frequency is 24 MHz, but can be configured for 48 MHz through I <sup>2</sup> C.                                    |

| 31, 30                                               | AGP[0:1]                                                                                                      | 0    | AGP Clock.                                                                                                                                                                                      |

| 34                                                   | SDATA                                                                                                         | I/O  | I <sup>2</sup> C Data. 5v tolerant                                                                                                                                                              |

| 35                                                   | SCLK                                                                                                          | I    | I <sup>2</sup> C Clock.5v tolerant                                                                                                                                                              |

| 33                                                   | PD#                                                                                                           | I    | Power-down Control. Turns off all clock outputs and shuts down device                                                                                                                           |

| 36                                                   | VDDA                                                                                                          | PWR  | 3.3V Analog Power/Ground. Power supply for core logic, PLL circuitry                                                                                                                            |

| 37                                                   | GNDA                                                                                                          | PWR  |                                                                                                                                                                                                 |

| 1, 5, 8, 11,<br>13, 18, 19,<br>24, 25, 28,<br>29, 32 | VDD_REF,<br>GND_REF,<br>GND_Z,<br>VDD_Z,<br>VDD_PCI,<br>GND_PCI,<br>GND_48,<br>VDD_48,<br>VDD_AGP,<br>GND_AGP | PWR  | 3.3V Power and Ground. Power supply for respective output buffers.                                                                                                                              |

| 38, 41, 42<br>48, 45                                 | VDD_CPU,<br>GND_CPU,<br>VDD_APIC,<br>GND_APIC                                                                 | PWR  | 2.5V Power and Ground. Power supply for respective output buffers.                                                                                                                              |

**Table 1. Frequency Selection Table**

| Input Co                                   | onditions |              | Output F      | requency     |              | VCO<br>Freq.<br>(MHz) |

|--------------------------------------------|-----------|--------------|---------------|--------------|--------------|-----------------------|

| I <sup>2</sup> C Option<br>(byte 4, bit 2) | FS(3:0)   | CPU<br>(MHz) | ZCLK<br>(MHz) | AGP<br>(MHz) | PCI<br>(MHz) |                       |

| 0                                          | 0000      | 133.3        | 66.7          | 66.7         | 33.3         | 400.0                 |

| 0                                          | 0001      | 133.3        | 66.7          | 50.0         | 33.3         | 400.0                 |

| 0                                          | 0010      | 133.3        | 100.0         | 66.7         | 33.3         | 400.0                 |

| 0                                          | 0011      | 133.3        | 100.0         | 50.0         | 33.3         | 400.0                 |

| 0                                          | 0100      | 133.3        | 133.3         | 66.7         | 33.3         | 400.0                 |

| 0                                          | 0101      | 133.3        | 133.3         | 50.0         | 33.3         | 400.0                 |

| 0                                          | 0110      | 133.3        | 166.6         | 66.7         | 33.3         | 666.5                 |

| 0                                          | 0111      | 133.3        | 166.6         | 55.5         | 33.3         | 666.5                 |

| 0 (defa                                    | ult) 1000 | 100.0        | 66.7          | 66.7         | 33.3         | 400.0                 |

| 0                                          | 1001      | 100.0        | 66.7          | 50.0         | 33.3         | 400.0                 |

| 0                                          | 1010      | 100.0        | 100.0         | 66.7         | 33.3         | 400.0                 |

| 0                                          | 1011      | 100.0        | 100.0         | 50.0         | 33.3         | 400.0                 |

| 0                                          | 1100      | 100.0        | 133.3         | 66.7         | 33.3         | 400.0                 |

| 0                                          | 1101      | 100.0        | 133.3         | 50.0         | 33.3         | 400.0                 |

| 0                                          | 1110      | 111.0        | 166.5         | 66.6         | 33.3         | 666.1                 |

| 0                                          | 1111      | 111.0        | 166.5         | 55.5         | 33.3         | 666.1                 |

| 1                                          | 0000      | 114.5        | 95.4          | 63.6         | 31.8         | 572.5                 |

| 1                                          | 0001      | 120.0        | 100.0         | 66.7         | 33.3         | 600.0                 |

| 1                                          | 0010      | 133.3        | 83.3          | 66.7         | 33.3         | 666.5                 |

| 1                                          | 0011      | 133.3        | 111.1         | 74.1         | 33.3         | 666.5                 |

| 1                                          | 0100      | 133.3        | 133.3         | 83.3         | 33.3         | 666.5                 |

| 1                                          | 0101      | 145.7        | 116.6         | 64.8         | 32.4         | 582.8                 |

| 1                                          | 0110      | 150.0        | 100.0         | 66.7         | 33.3         | 600.0                 |

| 1                                          | 0111      | 166.6        | 111.1         | 66.7         | 33.3         | 666.5                 |

| 1                                          | 1000      | 111.1        | 133.3         | 66.7         | 33.3         | 666.5                 |

| 1                                          | 1001      | 137.4        | 137.4         | 68.7         | 34.4         | 549.6                 |

| 1                                          | 1010      | 144.9        | 144.9         | 64.4         | 32.2         | 579.5                 |

| 1                                          | 1011      | 150.0        | 150.0         | 66.7         | 33.3         | 600.0                 |

| 1                                          | 1100      | 155.1        | 124.1         | 68.9         | 34.5         | 620.3                 |

| 1                                          | 1101      | 166.6        | 133.3         | 66.7         | 33.3         | 666.5                 |

| 1                                          | 1110      | 180.1        | 135.1         | 67.6         | 33.8         | 540.4                 |

| 1                                          | 1111      | 200.0        | 133.3         | 66.7         | 33.3         | 400.0                 |

#### **Serial Data Interface**

To enhance the flexibility and function of the clock synthesizer, a two-signal serial interface is provided. Through the Serial Data Interface, various device functions, such as individual clock output buffers, can be individually enabled or disabled. The registers associated with the Serial Data Interface initializes to their default setting upon power-up, and therefore use of this interface is optional. Clock device register changes are normally made upon system initialization, if any are required. The interface can also be used during system operation for power management functions.

#### **Data Protocol**

The clock driver serial protocol accepts byte write, byte read, block write, and block read operations from the controller. For block write/read operation, the bytes must be accessed in sequential order from lowest to highest byte (most significant bit first) with the ability to stop after any complete byte has been transferred. For byte write and byte read operations, the system controller can access individually indexed bytes. The offset of the indexed byte is encoded in the command code, as described in *Table 2*.

The block write and block read protocol is outlined in *Table 3* while *Table 4* outlines the corresponding byte write and byte read protocol. The slave receiver address is 11010010 (D2h).

**Table 2. Command Code Definition**

| Bit   | Description                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 7     | 0 = Block read or block write operation, 1 = Byte read or byte write operation                                              |

| (6:0) | Byte offset for byte read or byte write operation. For block read or block write operations, these bits should be '0000000' |

Table 3. Block Read and Block Write Protocol

|       | Block Write Protocol                                        |       | Block Read Protocol                                         |

|-------|-------------------------------------------------------------|-------|-------------------------------------------------------------|

| Bit   | Description                                                 | Bit   | Description                                                 |

| 1     | Start                                                       | 1     | Start                                                       |

| 2:8   | Slave address – 7 bits                                      | 2:8   | Slave address – 7 bits                                      |

| 9     | Write = 0                                                   | 9     | Write = 0                                                   |

| 10    | Acknowledge from slave                                      | 10    | Acknowledge from slave                                      |

| 11:18 | Command Code – 8 bits '00000000' stands for block operation | 11:18 | Command Code – 8 bits '00000000' stands for block operation |

| 19    | Acknowledge from slave                                      | 19    | Acknowledge from slave                                      |

| 20:27 | Byte Count – 8 bits                                         | 20    | Repeat start                                                |

| 28    | Acknowledge from slave                                      | 21:27 | Slave address – 7 bits                                      |

| 29:36 | Data byte 1 – 8 bits                                        | 28    | Read = 1                                                    |

| 37    | Acknowledge from slave                                      | 29    | Acknowledge from slave                                      |

| 38:45 | Data byte 2 – 8 bits                                        | 30:37 | Byte count from slave – 8 bits                              |

| 46    | Acknowledge from slave                                      | 38    | Acknowledge                                                 |

|       |                                                             | 39:46 | Data byte from slave – 8 bits                               |

|       | Data Byte (N-1) -8 bits                                     | 47    | Acknowledge                                                 |

|       | Acknowledge from slave                                      | 48:55 | Data byte from slave – 8 bits                               |

|       | Data Byte N –8 bits                                         | 56    | Acknowledge                                                 |

|       | Acknowledge from slave                                      |       | Data bytes from slave/Acknowledge                           |

|       | Stop                                                        |       | Data byte N from slave – 8 bits                             |

|       |                                                             |       | Not Acknowledge                                             |

|       |                                                             |       | Stop                                                        |

Table 4. Byte Read and Byte Write Protocol

|       | Byte Write Protocol                                                                                                                        |       | Byte Read Protocol                                                                                                                         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Description                                                                                                                                | Bit   | Description                                                                                                                                |

| 1     | Start                                                                                                                                      | 1     | Start                                                                                                                                      |

| 2:8   | Slave address – 7 bits                                                                                                                     | 2:8   | Slave address – 7 bits                                                                                                                     |

| 9     | Write = 0                                                                                                                                  | 9     | Write = 0                                                                                                                                  |

| 10    | Acknowledge from slave                                                                                                                     | 10    | Acknowledge from slave                                                                                                                     |

| 11:18 | Command Code – 8 bits '1xxxxxxx' stands for byte operation, bits[6:0] of the command code represents the offset of the byte to be accessed | 11:18 | Command Code – 8 bits '1xxxxxxx' stands for byte operation, bits[6:0] of the command code represents the offset of the byte to be accessed |

| 19    | Acknowledge from slave                                                                                                                     | 19    | Acknowledge from slave                                                                                                                     |

| 20:27 | Data byte from master – 8 bits                                                                                                             | 20    | Repeat start                                                                                                                               |

Document #: 38-07533 Rev. \*A Page 4 of 18

Table 4. Byte Read and Byte Write Protocol (continued)

|     | Byte Write Protocol    |       | Byte Read Protocol            |

|-----|------------------------|-------|-------------------------------|

| Bit | Description            | Bit   | Description                   |

| 28  | Acknowledge from slave | 21:27 | Slave address – 7 bits        |

| 29  | Stop                   | 28    | Read = 1                      |

|     |                        | 29    | Acknowledge from slave        |

|     |                        | 30:37 | Data byte from slave – 8 bits |

|     |                        | 38    | Not Acknowledge               |

|     |                        | 39    | Stop                          |

### **Device Configuration Map**

Data Bytes 0 to 3: Reserved for ZDB Registers

Byte 4

| Bit   | @Pup | Name                            |                                                                                                 | Description    |               |                      |

|-------|------|---------------------------------|-------------------------------------------------------------------------------------------------|----------------|---------------|----------------------|

| Bit 7 | 1    | Frequency Select Register (FS3) | Bit2 = 0 [74]                                                                                   | CPU            | ZCLK          | AGPPCI               |

| D:4 C | •    | 1 1                             | 0000                                                                                            | 133.3          | 66.7          | 66.733.3             |

| Bit 6 | 0    | Frequency Select Register       | 0001<br>0010                                                                                    | 133.3<br>133.3 | 66.7<br>100.0 | 50.033.3<br>66.733.3 |

|       |      | (FS2)                           | 0010                                                                                            | 133.3          | 100.0         | 50.033.3             |

| Bit 5 | 0    | Frequency Select Register       | 0100                                                                                            | 133.3          | 133.3         | 66.733.3             |

| DIL 3 | U    |                                 | 0100                                                                                            | 133.3          | 133.3         | 50.033.3             |

|       |      | (FS1)                           | 0110                                                                                            | 133.3          | 166.6         | 66.733.3             |

| Bit 4 | 0    | Frequency Select Register       | 0111                                                                                            | 133.3          | 166.6         | 55.533.3             |

| DIL 4 | U    |                                 | 1000                                                                                            | 100.0          | 66.7          | 66.733.3             |

|       |      | (FS0)                           | 1001                                                                                            | 100.0          | 66.7          | 50.033.3             |

|       |      |                                 | 1010                                                                                            | 100.0          | 100.0         | 66.733.3             |

|       |      |                                 | 1010                                                                                            | 100.0          | 100.0         | 50.033.3             |

|       |      |                                 | 1100                                                                                            | 100.0          | 133.3         | 66.733.3             |

|       |      |                                 | 1101                                                                                            | 100.0          | 133.3         | 50.033.3             |

|       |      |                                 | 1110                                                                                            | 111.0          | 166.5         | 66.633.3             |

|       |      |                                 | 1111                                                                                            | 111.0          | 166.5         | 55.533.3             |

|       |      |                                 | Bit2 = 1                                                                                        | 111.0          | 100.0         | 00.000.0             |

|       |      |                                 | 0000                                                                                            | 114.5          | 95.4          | 63.631.8             |

|       |      |                                 | 0001                                                                                            | 120.0          | 100.0         | 66.733.3             |

|       |      |                                 | 0010                                                                                            | 133.3          | 83.3          | 66.733.3             |

|       |      |                                 | 0011                                                                                            | 133.3          | 111.1         | 74.133.3             |

|       |      |                                 | 0100                                                                                            | 133.3          | 133.3         | 83.333.3             |

|       |      |                                 | 0101                                                                                            | 145.7          | 116.6         | 64.832.4             |

|       |      |                                 | 0110                                                                                            | 150.0          | 100.0         | 66.733.3             |

|       |      |                                 | 0111                                                                                            | 166.6          | 111.1         | 66.733.3             |

|       |      |                                 | 1000                                                                                            | 111.1          | 133.3         | 66.733.3             |

|       |      |                                 | 1001                                                                                            | 137.4          | 137.4         | 68.734.4             |

|       |      |                                 | 1010                                                                                            | 144.9          | 144.9         | 64.432.2             |

|       |      |                                 | 1011                                                                                            | 150.0          | 150.0         | 66.733.3             |

|       |      |                                 | 1100                                                                                            | 155.1          | 124.1         | 68.934.5             |

|       |      |                                 | 1101                                                                                            | 166.6          | 133.3         | 66.733.3             |

|       |      |                                 | 1110                                                                                            | 180.1          | 135.1         | 67.633.8             |

|       |      |                                 | 1111                                                                                            | 200.0          | 133.3         | 66.733.3             |

| Bit 3 | 0    | FS_Override                     | Frequency Selection Source:<br>0 = Select through hardwa<br>1 = Select through I <sup>2</sup> C |                | , latched     | inputs               |

| Bit 2 | 0    | Frequency Select Register       | Most significant bit of I <sup>2</sup> C Frequency Select Register                              |                |               |                      |

| Bit 1 | 1    | Spread Spectrum Control         | 0 = Normal, 1 = Spread S                                                                        | •              | ole           |                      |

| Bit 0 | 0    | Output Disable                  | 0 = Normal, 1 = three-stat                                                                      | te all outputs |               |                      |

### Byte 5

| Bit   | @Pup | Name     | Description |

|-------|------|----------|-------------|

| Bit 7 | 0    | Reserved | Reserved    |

| Bit 6 | 0    | Reserved | Reserved    |

| Bit 5 | 0    | Reserved | Reserved    |

| Bit 4 | 0    | Reserved | Reserved    |

Document #: 38-07533 Rev. \*A Page 5 of 18

# Byte 5 (continued)

| Bit   | @Pup | Name              | Description                                       |

|-------|------|-------------------|---------------------------------------------------|

| Bit 3 | HW   | Latched FS3 input | Latched FS[3:0] inputs. These bits are read-only. |

| Bit 2 | HW   | Latched FS2 input |                                                   |

| Bit 1 | HW   | Latched FS1 input |                                                   |

| Bit 0 | HW   | Latched FS0 input |                                                   |

### Byte 6

| Bit   | @Pup | Name        | Description                                                                         |

|-------|------|-------------|-------------------------------------------------------------------------------------|

| Bit 7 | 0    | Reserved    | Reserved                                                                            |

| Bit 6 | 0    | Reserved    | Reserved                                                                            |

| Bit 5 | 0    | PCIF0       | PCIF0 functionality when PCI_STP# is LOW 0: Free running, 1: Stop                   |

| Bit 4 | 0    | PCIF1       | PCIF1 functionality when PCI_STP# is LOW 0: Free running, 1: Stop                   |

| Bit 3 | 1    | CPUT0/CPUC0 | CPU[T/C]0 functionality when CPU_STP# is LOW 0: Free running, 1: Stop (three-state) |

| Bit 2 | 0    | CPUT1       | CPUT1 functionality when CPU_STP# is LOW 0: Free running, 1: Stop (three-state)     |

| Bit 1 | 1    | CPUT0/CPUC0 | CPU[T/C]0 Output Enable/Disable                                                     |

| Bit 0 | 1    | CPUT1       | CPUT1 Output Enable/Disable                                                         |

### Byte 7

| Bit   | @Pup | Name  | Description                 |

|-------|------|-------|-----------------------------|

| Bit 7 | 1    | PCIF1 | PCIF1 Output Enable/Disable |

| Bit 6 | 1    | PCIF0 | PCIF0 Output Enable/Disable |

| Bit 5 | 1    | PCI_5 | PCI_5 Output Enable/Disable |

| Bit 4 | 1    | PCI_4 | PCI_4 Output Enable/Disable |

| Bit 3 | 1    | PCI_3 | PCI_3 Output Enable/Disable |

| Bit 2 | 1    | PCI_2 | PCI_2 Output Enable/Disable |

| Bit 1 | 1    | PCI_1 | PCI_1 Output Enable/Disable |

| Bit 0 | 1    | PCI_0 | PCI_0 Output Enable/Disable |

### Byte 8

| Bit   | @Pup | Name         | Pin Description                                                     |

|-------|------|--------------|---------------------------------------------------------------------|

| Bit 7 | 1    | Vendor_ID3   | Bit[3] of Cypress Semiconductor's Vendor ID. This bit is read only. |

| Bit 6 | 0    | Vendor_ID2   | Bit[2] of Cypress Semiconductor's Vendor ID. This bit is read only. |

| Bit 5 | 0    | Vendor_ID1   | Bit[1] of Cypress Semiconductor's Vendor ID. This bit is read only. |

| Bit 4 | 0    | Vendor_ID0   | Bit[0] of Cypress Semiconductor's Vendor ID. This bit is read only. |

| Bit 3 | 0    | Revision_ID3 | Revision ID bit[3]                                                  |

| Bit 2 | 0    | Revision_ID2 | Revision ID bit[2]                                                  |

| Bit 1 | 0    | Revision_ID1 | Revision ID bit[1]                                                  |

| Bit 0 | 0    | Revision_ID0 | Revision ID bit[0]                                                  |

## Byte 9

| Bit   | @Pup | Name     | Description           |  |  |

|-------|------|----------|-----------------------|--|--|

| Bit 7 | 1    | PD#      | Power-down Enable     |  |  |

| Bit 6 | 0    | Reserved | Reserved              |  |  |

| Bit 5 | 1    | 48MHz    | 48-MHz Output Control |  |  |

Document #: 38-07533 Rev. \*A Page 6 of 18

# Byte 9 (continued)

| Bit   | @Pup | Name     | Description                                                                                                                                                                         |  |  |  |

|-------|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit 4 | 1    | 24_48MHz | 24_48MHz Output Control                                                                                                                                                             |  |  |  |

| Bit 3 | 0    | 24_48MHz | 24-MHz or 48-MHz Select<br>0: 24MHz, 1: 48MHz                                                                                                                                       |  |  |  |

| Bit 2 | 0    | SS2      | Spread Spectrum control bit (0 = down spread, 1 = center spread)                                                                                                                    |  |  |  |

| Bit 1 | 0    | SS1      | SS[2:0] Spread Mode Spread% 000 Down 0, -0.50 (default)                                                                                                                             |  |  |  |

| Bit 0 | 0    | SS0      | 001 Down +0.12, -0.62<br>010 Down +0.25, -0.75<br>011 Down +0.50, -1.00<br>100 Center +0.25, -0.25<br>101 Center +0.37, -0.37<br>110 Center +0.50, -0.50<br>111 Center +0.75, -0.75 |  |  |  |

## Byte 10

| Bit   | @Pup | Name     | Description             |

|-------|------|----------|-------------------------|

| Bit 7 | 1    | IOAPIC_1 | IOAPIC_1 Output Control |

| Bit 6 | 1    | IOAPIC_0 | IOAPIC_0 Output Control |

| Bit 5 | 1    | REF_1    | REF_1 Output Control    |

| Bit 4 | 1    | REF_0    | REF_0 Output Control    |

| Bit 3 | 1    | ZCLK_1   | ZCLK_1 Output Control   |

| Bit 2 | 1    | ZCLK_0   | ZCLK_0 Output Control   |

| Bit 1 | 1    | AGP_1    | AGP_1 Output Control    |

| Bit 0 | 1    | AGP_0    | AGP_0 Output Control    |

## Byte 11

| Bit   | @Pup | Name              | Description                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-------|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit 7 | 0    | Reserved          | Vendor Test Mode (always program to 0)                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Bit 6 | 0    | Reserved          | Vendor Test Mode (always program to 0)                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Bit 5 | 0    | Reserved          | Vendor Test Mode (always program to 0)                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Bit 4 | 0    | 3V66 Fract_Align4 | 3V66 Frequency Fractional Aligner: These bits determine the 3V66 fixed                                                                                                                                                                                                                                                                                        |  |  |  |

| Bit 3 | 0    | 3V66 Fract_Align3 | frequency. This option does not incorporate spread spectrum.  Fract Align3V66 (MHz)PCI (MHz)                                                                                                                                                                                                                                                                  |  |  |  |

| Bit 2 | 0    | 3V66 Fract_Align2 | 0000 Off Off(default)<br>0000166.533.2                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Bit 1 | 0    | 3V66 Fract_Align1 | 0001067.533.7<br>0001168.534.3                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Bit 0 | 0    | 3V66 Fract_Align0 | 0010069.534.8 0010170.635.3 0011071.635.8 0011172.636.3 0100073.636.8 0101075.737.8 0101075.737.8 0101076.738.4 0110077.738.9 0110178.739.4 0111079.839.9 0111180.840.4 1000081.840.9 1000182.841.4 1001083.941.9 1001184.942.4 1010085.943.0 1010186.943.5 1011088.044.0 1011189.044.5 1100090.045.0 1100191.045.5 1110094.147.0 1111095.147.6 1111096.148.1 |  |  |  |

# Byte 12

| Bit   | @Pup | Name           | Description                                                                                                                                                    |  |  |  |

|-------|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit 7 | 0    | REF_2          | REF_2 Output Control (default: off)                                                                                                                            |  |  |  |

| Bit 6 | 0    | Reserved       | Reserved                                                                                                                                                       |  |  |  |

| Bit 5 | 0    | Reserved       | Reserved                                                                                                                                                       |  |  |  |

| Bit 4 | 0    | DARAG2         | Dial-a-Ratio™ AGP[0:1].                                                                                                                                        |  |  |  |

| Bit 3 | 0    | DARAG1         | Programming these bits allow modifying the frequency ratio of the AGP(1:0), PCI(5:0) and PCIF(0:1) clocks relative to the VCO. (the ratio                      |  |  |  |

| Bit 2 | 0    | DARAG0         | of AGP to PCI is retained at 2:1)  DARAG[2:0] VC0/AGP Ratio  000 - (Frequency Selection Default)  010 8  011 9  100 10  101 12  110 12  111 12                 |  |  |  |

| Bit 1 | 0    | Fixed_PCI_SEL  | PCI output frequency select mode (valid only when Fixed_3V66_SEL = 1) 0 = Use Frequency Selection Table settings 1 = Use Fractional Aligner settings (default) |  |  |  |

| Bit 0 | 0    | Fixed_3V66_SEL | 3V66 and PCI output frequency select mode 0 = Use Frequency Selection Table settings (default) 1 = Use Fractional Aligner settings                             |  |  |  |

## Byte 13

| Bit   | @Pup | Name     | Description                                                                                                                                      |

|-------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7 | 0    | Reserved | Reserved                                                                                                                                         |

| Bit 6 | 0    | N6 (MSB) | Dial-a-Frequency® Control Register N. These bits are for programming                                                                             |

| Bit 5 | 0    | N5       | the PLL's internal N register. This access allows the user to modify the CPU frequency with great accuracy. All other synchronous clocks (clocks |

| Bit 4 | 0    | N4       | that are generated from the same PLL, such as PCI, remain at their                                                                               |

| Bit 3 | 0    | N3       | existing ratios relative to the CPU clock. (should be written together with                                                                      |

| Bit 2 | 0    | N2       | Control Register R)                                                                                                                              |

| Bit 1 | 0    | N1       |                                                                                                                                                  |

| Bit 0 | 0    | N0 (LSB) |                                                                                                                                                  |

## Byte 14

| Bit   | @Pup | Name         | Pin Description                                                                                                                                                                          |  |  |

|-------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit 7 | 0    | Reserved     | Reserved                                                                                                                                                                                 |  |  |

| Bit 6 | 0    | R5 (MSB)     | Dial-a-Frequency Control Register R                                                                                                                                                      |  |  |

| Bit 5 | 0    | R4           | These bits are for programming the PLL's internal R register. This access                                                                                                                |  |  |

| Bit 4 | 0    | R3           | <ul> <li>allows the user to modify the CPU frequency with great accuracy. All of synchronous clocks (clocks that are generated from the same PLL, see the synchronous clocks)</li> </ul> |  |  |

| Bit 3 | 0    | R2           | as PCI, remain at their existing ratios relative to the CPU clock.                                                                                                                       |  |  |

| Bit 2 | 0    | R1           | (should be written together with Control Register N)                                                                                                                                     |  |  |

| Bit 1 | 0    | R0 (LSB)     |                                                                                                                                                                                          |  |  |

| Bit 0 | 0    | R & N Select | R and N register mux selection. 0 = R and N values come from the ROM. 1 = data is loaded from the DAF registers into R and N.                                                            |  |  |

Document #: 38-07533 Rev. \*A

#### **Dial-A-Frequency Feature**

SMBus Dial-a-Frequency feature is available in this device via Byte13 and Byte14. P is a large value PLL constant that depends on the frequency selection achieved through the hardware selectors (FS). P value may be determined from the following table.

| FS(4:0)                                                                                          | Р         |

|--------------------------------------------------------------------------------------------------|-----------|

| 00000, 00001, 00010, 00011, 00100, 00101, 11110                                                  | 127993333 |

| 00110, 00111, 10000, 10001, 10010, 10011, 10100                                                  | 76796000  |

| 01000, 01001, 01010, 01011, 01100, 01101, 10101, 10110, 10111, 11001, 11010, 11011, 11100, 11101 | 95995000  |

| 01110, 01111, 11000                                                                              | 63996667  |

| 11111                                                                                            | 191990000 |

**Table 5. Maximum Lumped Capacitive Output Loads**

| Clock           | Max Load     | Unit |

|-----------------|--------------|------|

| PCI, PCIF       | 20           | pF   |

| AGP             | 30           | pF   |

| 24_48MHz, 48MHz | 20           | pF   |

| REF             | 30           | pF   |

| IOAPIC          | 20           | pF   |

| CPUT0/CPUC0     | See Figure 7 |      |

| CPUT1           | See Figure 7 |      |

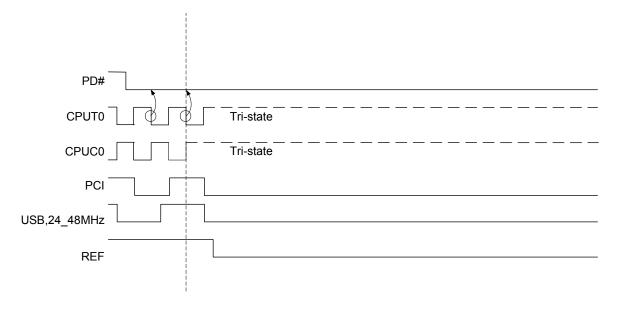

#### PD# (Power-down) Clarification

The PD# (Power-down) pin is used to shut off ALL clocks prior to shutting off power to the device. PD# is an asynchronous active LOW input. This signal is synchronized internally to the device powering down the clock synthesizer. PD# is an asynchronous function for powering up the system. When PD# is low, all clocks are driven to a LOW value and held there and the VCO and PLLs are also powered down. All clocks are shut down in a synchronous manner so has not to cause glitches while transitioning to the low 'stopped' state.

PD# - Assertion

Figure 1. Power-down Assertion Timing Waveforms

#### PD# - Deassertion

After the clock chip internal PLL is powered up and locked, all outputs will be enabled within a few clock cycles of each other, with the first to last active clock taking no more than two full PCI clock cycles.

Figure 2. Power Down Deassertion Timing Waveforms

Table 6. PD# Functionality

| PD# | CPUT   | CPUC   | AGP    | PCIF/PCI | 48MHz  |

|-----|--------|--------|--------|----------|--------|

| 1   | Normal | Normal | Normal | Normal   | Normal |

| 0   | Float  | Float  | Low    | Low      | Low    |

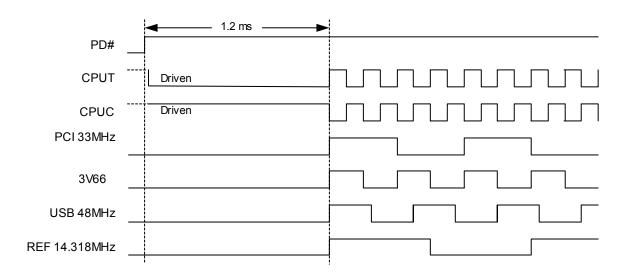

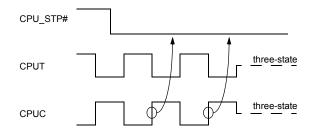

#### CPU\_STP# Clarification

The CPU\_STP# signal is an active LOW input used for synchronous stopping and starting the CPU output clocks while the rest of the clock generator continues to function.

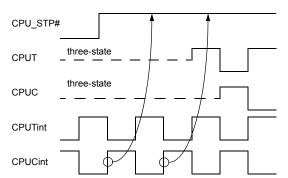

#### CPU\_STP# - Assertion

When CPU\_STP# pin is asserted, all CPUT/C outputs that are set with the SMBus configuration to be stoppable via assertion of CPU\_STP# will be stopped after being sampled by two rising CPUC clock edges. The final state of the stopped CPU signals is CPUT = CPUC = three-state.

Figure 3. CPU\_STP# Assertion Waveform

#### CPU\_STP# Deassertion

The deassertion of the CPU\_STP# signal will cause all CPUT/C outputs that were stopped to resume normal operation in a synchronous manner. Synchronous manner meaning that no short or stretched clock pulses will be produced when the clock resumes. The maximum latency from the deassertion to active outputs is no more than two CPUC clock cycles.

Figure 4. CPU\_STP# Deassertion Waveform

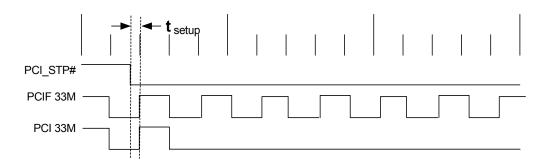

#### PCI\_STP# Assertion

The PCI\_STP# signal is an active LOW input used for synchronous stopping and starting the PCI outputs while the rest of the clock generator continues to function. The set-up time for capturing PCI\_STP# going LOW is 10 ns ( $t_{setup}$ ). The PCIF clocks will not be affected by this pin if their control bits in the SMBus register are set to allow them to be free running.

Figure 5. PCI\_STP# Assertion Waveform

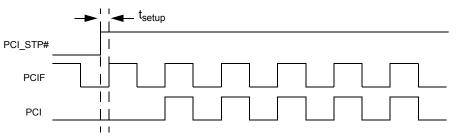

#### PCI\_STP# - Deassertion

The deassertion of the PCI\_STP# signal will cause all PCI and stoppable PCIF clocks to resume running in a synchronous manner within two PCI clock periods after PCI\_STP# transitions to a high level.

Figure 6. PCI\_STP# Deassertion Waveform

### **Absolute Maximum Conditions**

| Parameter          | Description                                          | Condition                                   | Min.             | Max.                  | Unit |

|--------------------|------------------------------------------------------|---------------------------------------------|------------------|-----------------------|------|

| $V_{DD}$           | Core Supply Voltage                                  |                                             | -0.5             | 4.6                   | V    |

| $V_{DDA}$          | Analog Supply Voltage                                |                                             | -0.5             | 4.6                   | V    |

| V <sub>IN</sub>    | Input Voltage                                        | Relative to V <sub>SS</sub>                 | -0.5             | V <sub>DD</sub> + 0.5 | VDC  |

| T <sub>S</sub>     | Temperature, Storage                                 | Non-functional                              | -65              | +150                  | °C   |

| T <sub>A</sub>     | Temperature, Operating Ambient                       | Functional                                  | 0                | 70                    | °C   |

| T <sub>J</sub>     | Temperature, Junction                                | Functional                                  | -                | 150                   | °C   |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model)                    | MIL-STD-883, Method 3015                    | 2000             | _                     | V    |

| Ø <sub>JC</sub>    | Dissipation, Junction to Case                        | Mil-Spec 883E Method 1012.1                 | •                | 15                    | °C/W |

| Ø <sub>JA</sub>    | Dissipation, Junction to Ambient                     | JEDEC (JESD 51)                             | 45               |                       | °C/W |

| UL-94              | Flammability Rating                                  | At 1/8 in.                                  | V-0              |                       |      |

| MSL                | Moisture Sensitivity Level 1                         |                                             |                  |                       |      |

| Multiple Supplies  | s: The voltage on any input or I/O pin cannot exceed | I the power pin during power-up. Power supp | ly sequencing is | NOT required.         |      |

## **DC Electrical Specifications**

| Parameter         | Description               | Conditions                                  | Min.               | Max.               | Unit |

|-------------------|---------------------------|---------------------------------------------|--------------------|--------------------|------|

| $V_{DD}, V_{DDA}$ | 3.3 Operating Voltage     | 3.3V ± 5%                                   | 3.135              | 3.465              | V    |

| C <sub>IN</sub>   | Input Pin Capacitance     |                                             | 2                  | 5                  | pF   |

| C <sub>OUT</sub>  | Output Pin Capacitance    |                                             | 3                  | 6                  | pF   |

| L <sub>IN</sub>   | Pin Inductance            |                                             | -                  | 7                  | nH   |

| I <sub>DD</sub>   | Dynamic Supply Current    | All frequencies at maximum value            | -                  | 280                | mA   |

| I <sub>PD</sub>   | Power-down Supply Current | PD# Asserted                                | -                  | 1                  | mA   |

| C <sub>XTAL</sub> | Crystal Pin Capacitance   | Measured from the XIN or XOUT pin to ground | 30                 | 42                 | pF   |

| V <sub>XIH</sub>  | XIN High Voltage          |                                             | 0.7V <sub>DD</sub> | $V_{DD}$           | V    |

| V <sub>XIL</sub>  | XIN Low Voltage           |                                             | 0                  | 0.3V <sub>DD</sub> | V    |

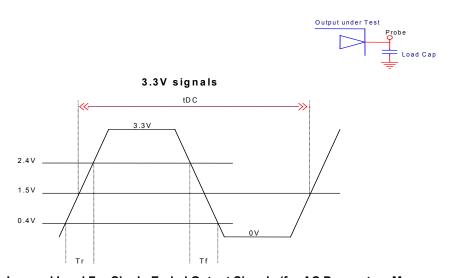

### **AC Electrical Specifications**

| Parameter                       | Description                  | Conditions                                                                                                                        | Min.   | Max. | Unit |

|---------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------|------|------|

|                                 | •                            | Crystal                                                                                                                           |        |      |      |

| T <sub>DC</sub>                 | XIN Duty Cycle               | The device will operate reliably with input duty cycles up to 30/70 but the REF clock duty cycle will not be within specification | 47.5   | 52.5 | %    |

| T <sub>PERIOD</sub>             | XIN Period                   | When Xin is driven from an external clock source                                                                                  | 69.841 | 71.0 | ns   |

| T <sub>R</sub> / T <sub>F</sub> | XIN Rise and Fall Times      | Measured between 0.3V <sub>DD</sub> and 0.7V <sub>DD</sub>                                                                        | -      | 10.0 | ns   |

| T <sub>CCJ</sub>                | XIN Cycle to Cycle Jitter    | As an average over 1-μs duration                                                                                                  | -      | 500  | ps   |

|                                 | С                            | PUT0/CPUC0                                                                                                                        |        |      |      |

| T <sub>DC</sub>                 | CPUT0 and CPUC0 Duty Cycle   | Measured at crossing point V <sub>OX</sub>                                                                                        | 45     | 55   | %    |

| T <sub>PERIOD</sub>             | 100-MHz CPUT and CPUC Period | Measured at crossing point V <sub>OX</sub>                                                                                        | 9.8    | 10.2 | ns   |

| T <sub>PERIOD</sub>             | 133-MHz CPUT and CPUC Period | Measured at crossing point V <sub>OX</sub>                                                                                        | 7.35   | 7.65 | ns   |

| T <sub>SKEW</sub>               | Any CPU to CPU Clock Skew    | Measured at crossing point V <sub>OX</sub>                                                                                        | -      | 150  | ps   |

| T <sub>CCJ</sub>                | CPU Cycle to Cycle Jitter    | Measured at crossing point V <sub>OX</sub>                                                                                        | -      | 150  | ps   |

Document #: 38-07533 Rev. \*A

# AC Electrical Specifications (continued)

| Parameter                          | ·                                                                              |                                                     | Min. | Max. | Unit |

|------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------|------|------|------|

| T <sub>R</sub> / T <sub>F</sub>    | CPUT and CPUC Rise and Fall Times Measured from Vol= 0.175 to Voh = 0.525V     |                                                     | 0.5  | 2.0  | V/ns |

| V <sub>OX</sub>                    | Crossing Point Voltage at 0.7V Swing                                           |                                                     | 600  | 800  | mv   |

|                                    | •                                                                              | CPUT1                                               |      |      |      |

| $T_{DC}$                           | CPUT1 Duty Cycle                                                               | Measured at crossing point V <sub>OX</sub>          | 45   | 55   | %    |

| T <sub>PERIOD</sub>                | 100MHz CPUT1 Period                                                            | Measured at crossing point V <sub>OX</sub>          | 9.8  | 10.2 | ns   |

| T <sub>PERIOD</sub>                | 133MHz CPUT1 Period                                                            | Measured at crossing point V <sub>OX</sub>          | 7.35 | 7.65 | ns   |

| T <sub>CCJ</sub>                   | CPUT1 Cycle to Cycle Jitter                                                    | Measured at crossing point V <sub>OX</sub>          | -    | 150  | ps   |

| T <sub>R</sub> / T <sub>F</sub>    | CPUT and CPUC Rise and Fall Times                                              | Measured from $V_{OL}$ = 0.175 to $V_{OH}$ = 0.525V | 0.5  | 2.0  | V/ns |

|                                    |                                                                                | IOAPIC                                              |      |      | _    |

| T <sub>DC</sub>                    | IOAPIC Duty Cycle                                                              | Measured at crossing point V <sub>OX</sub>          | 45   | 55   | %    |

| T <sub>PERIOD</sub>                | 100MHz IOAPIC Period                                                           | Measured at crossing point V <sub>OX</sub>          | 69   | 70   | ns   |

| T <sub>PERIOD</sub>                | 133MHz IOAPIC Period                                                           | Measured at crossing point V <sub>OX</sub>          | 69   | 70   | ns   |

| T <sub>SKEW</sub>                  | Any IOAPIC clock to any IOPIC Clock Skew                                       | Measured at crossing point V <sub>OX</sub>          | -    | 250  | ps   |

| T <sub>HIGH</sub>                  | IOAPIC High Time                                                               |                                                     | 25.5 | -    |      |

| T <sub>LOW</sub>                   | IOAPIC Low Time                                                                |                                                     | 25.3 | -    |      |

| T <sub>CCJ</sub>                   | IOAPIC Cycle to Cycle Jitter                                                   | Measured at crossing point V <sub>OX</sub>          | _    | 500  | ps   |

| T <sub>R</sub> / T <sub>F</sub>    | IOAPIC Rise and Fall Times                                                     | Measured from Vol= 0.175 to<br>Voh = 0.525V         | 0.4  | 1.6  | V/ns |

|                                    |                                                                                | AGP                                                 |      | •    |      |

| T <sub>DC</sub>                    | AGP Duty Cycle                                                                 | Measured at crossing point V <sub>OX</sub>          | 45   | 55   | %    |

| T <sub>PERIOD</sub>                | 100-MHz AGP Period Measured at crossin                                         |                                                     | 15.0 | 15.3 | ns   |

| T <sub>PERIOD</sub>                | 133-MHz AGP Period Measured at crossing point V <sub>OX</sub>                  |                                                     | 15.0 | 15.3 | ns   |

| T <sub>SKEW(UNBUF-</sub><br>FERED) | Any AGP clock to any AGP Clock Skew Measured at crossing point V <sub>OX</sub> |                                                     | -    | 250  | ps   |

| T <sub>HIGH</sub>                  | AGP High Time                                                                  |                                                     | 5.25 | -    | ns   |

| T <sub>LOW</sub>                   | AGP Low Time                                                                   |                                                     | 5.25 | -    | ns   |

| T <sub>CCJ</sub>                   | AGP Cycle to Cycle Jitter                                                      | Measured at crossing point V <sub>OX</sub>          | _    | 250  | ps   |

| T <sub>R</sub> / T <sub>F</sub>    | AGP Rise and Fall Times                                                        | Measured from Vol = 0.175 to<br>Voh = 0.525V        | 0.5  | 1.6  | ns   |

|                                    | •                                                                              | ZCLK                                                |      |      |      |

| T <sub>DC</sub>                    | ZCLK Duty Cycle                                                                | Measured at crossing point V <sub>OX</sub>          | 45   | 55   | %    |

| T <sub>SKEW</sub>                  | Any ZCLK clock to any ZCLK Clock Skew                                          | Measured at crossing point V <sub>OX</sub>          | _    | 175  | ps   |

| T <sub>CCJ</sub>                   | ZCLK Cycle to Cycle Jitter                                                     | Measured at crossing point V <sub>OX</sub>          | _    | 250  | ps   |

| T <sub>R</sub> / T <sub>F</sub>    | ZCLK Rise and Fall Times                                                       | Measured from Vol= 0.175 to<br>Voh = 0.525V         | 0.5  | 1.6  | ns   |

|                                    |                                                                                | PCI/PCIF                                            |      |      |      |

| T <sub>DC</sub>                    | PCI and PCIF Duty Cycle Measured at crossing point V <sub>O</sub>              |                                                     | 45   | 55   | %    |

| T <sub>PERIOD</sub>                | 100-MHz PCI and PCIF Period                                                    | Measured at crossing point V <sub>OX</sub>          | 30.0 | _    | ns   |

| T <sub>PERIOD</sub>                | 133-MHz PCI and PCIF Period                                                    | Measured at crossing point V <sub>OX</sub>          | 30.0 |      | ns   |

| T <sub>SKEW</sub>                  | Any PCI and PCIF clock to any PCI and PCIF Clock Skew                          | Measured at crossing point V <sub>OX</sub>          | _    | 500  | ps   |

| T <sub>HIGH</sub>                  | PCI and PCIF High Time                                                         |                                                     | 12.0 | -    | ns   |

| T <sub>LOW</sub>                   | PCI and PCIF Low Time                                                          |                                                     | 12.0 | _    | ns   |

# AC Electrical Specifications (continued)

| Parameter                       | Description Conditions                |                                            | Min.   | Max.     | Unit |  |

|---------------------------------|---------------------------------------|--------------------------------------------|--------|----------|------|--|

| T <sub>CCJ</sub>                | PCI and PCIF Cycle to Cycle Jitter    | Measured at crossing point V <sub>OX</sub> | -      | 500      | ps   |  |

| T <sub>R</sub> / T <sub>F</sub> | PCI and PCIF Rise and Fall Times      | Measured from Vol= 0.175 to Voh = 0.525V   | 0.5    | 2.0      | ns   |  |

|                                 |                                       | 48M                                        |        |          |      |  |

| T <sub>DC</sub>                 | 48M Duty Cycle                        | Measurement at 1.5V                        | 45     | 45 55    |      |  |

| T <sub>PERIOD</sub>             | 133-MHz 48M Period                    | Measurement at 1.5V                        | 20.829 | 20.834   | ns   |  |

| T <sub>PERIOD</sub>             | 133-MHz 48 M Period                   | Measurement at 1.5V                        | 20.829 | 20.834   | ns   |  |

| T <sub>R</sub> / T <sub>F</sub> | 48M Rise and Fall Times               | Measured between 0.4V and 2.4V             | 1.0    | 2.0      | ns   |  |

| T <sub>CCJ</sub>                | 48M Cycle to Cycle Jitter             | Measurement at 1.5V                        | _      | 350      | ps   |  |

|                                 |                                       | 24M                                        |        |          |      |  |

| T <sub>DC</sub>                 | 24M Duty Cycle                        | Measurement at 1.5V                        | 45     | 55       | %    |  |

| T <sub>PERIOD</sub>             | 100-MHz 24M Period                    | Measurement at 1.5V                        | 41.66  | 41.67    | ns   |  |

| T <sub>PERIOD</sub>             | 133-MHz 24M Period                    | Measurement at 1.5V                        | 41.66  | 41.67    | ns   |  |

| T <sub>R</sub> / T <sub>F</sub> | 24M Rise and Fall Times               | Measured between 0.4V and 2.4V             | 1.0    | 2.0      | ns   |  |

| T <sub>CCJ</sub>                | 24M Cycle to Cycle Jitter             | Measurement at 1.5V                        | _      | 500      | ps   |  |

|                                 |                                       | REF                                        |        | l e      | L    |  |

| T <sub>DC</sub>                 | REF Duty Cycle                        | Measurement at 1.5V                        | 45     | 55       | %    |  |

| T <sub>PERIOD</sub>             | REF Period                            | Measurement at 1.5V                        | 69.841 | 71.0     | ns   |  |

| T <sub>R</sub> / T <sub>F</sub> | REF Rise and Fall Times               | Measured between 0.4V and 2.4V             | 1.0    | 4.0      | ns   |  |

| T <sub>CCJ</sub>                | REF Cycle to Cycle Jitter             | Measurement at 1.5V                        | _      | 1000     | ps   |  |

|                                 | ENABLE/I                              | DISABLE and SETUP                          |        | <u> </u> |      |  |

| T <sub>STABLE</sub>             | All Clock Stabilization from Power-up |                                            | _      | 1.5      | ms   |  |

| T <sub>SS</sub>                 | Stopclock Set-up Time                 |                                            | 10.0   | -        | ns   |  |

| T <sub>SH</sub>                 | Stopclock Hold Time                   |                                            | 0      | -        | ns   |  |

| T <sub>ODIS</sub>               | Output Disable Delay (all outputs)    |                                            | 1.0    | 10.00    | ns   |  |

| T <sub>OENB</sub>               | Output Enable Delay (all outputs)     |                                            | 1.0    | 10.00    | ns   |  |

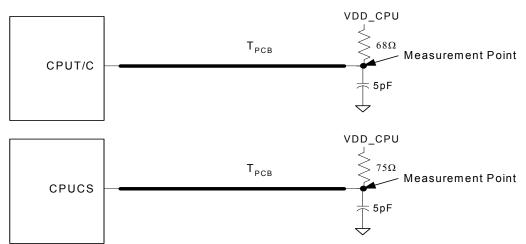

### **Test and Measurement Set-up**

For Differential CPU Output Signals

The following diagram shows lumped test load configurations for the differential Host Clock Outputs.

Figure 7. CPUCLK Test Load Configuration

Figure 8. Lumped Load For Single-Ended Output Signals (for AC Parameters Measurement)

Table 7. Group Timing Relationship and Tolerances

|            | Offset (Typical) | Tolerance (or Range) | Conditions | Notes |

|------------|------------------|----------------------|------------|-------|

| CPU to AGP | 2 ns             | 1 – 4 ns             | CPU leads  | _     |

| CPU to Z   | 2 ns             | 1 – 4 ns             | CPU leads  | _     |

| CPU to PCI | 2 ns             | 1 – 4 ns             | CPU leads  | 1     |

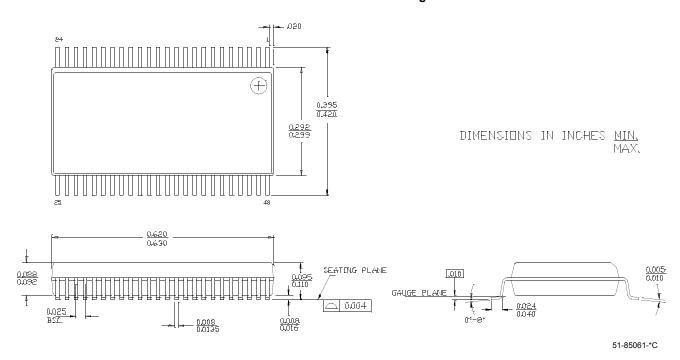

### **Ordering Information**

| Ordering Code                                        | Package Type                                               | Operating Range         |  |

|------------------------------------------------------|------------------------------------------------------------|-------------------------|--|

| CY28372OC 48-pin Small Shrunk Outline Package (SSOP) |                                                            | Commercial, 0°C to 70°C |  |

| CY28372OCT                                           | 48-pin Small Shrunk Outline Package (SSOP) – Tape and Reel | Commercial, 0°C to 70°C |  |

| Lead Free                                            |                                                            |                         |  |

| CY28372OXC                                           | 48-pin Small Shrunk Outline Package (SSOP)                 | Commercial, 0°C to 70°C |  |

| CY28372OXCT                                          | 48-pin Small Shrunk Outline Package (SSOP) – Tape and Reel | Commercial, 0°C to 70°C |  |

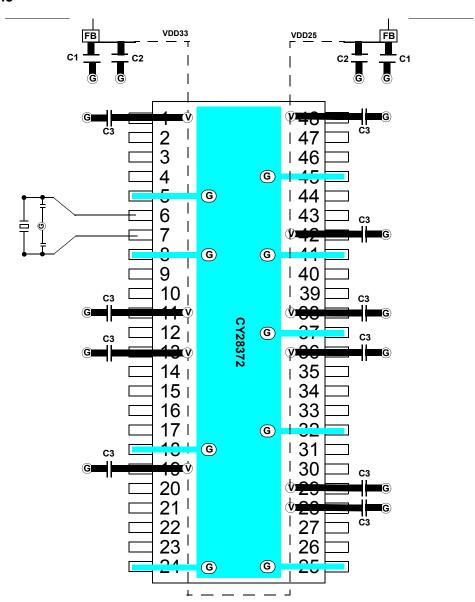

### **Layout Example**

$\label{eq:continuous} FB = \text{Dale ILB1206 - } 300~(300~\Omega~@~100~\text{MHz})$  Cermaic Caps C1 = 10 - 22  $\mu F$  C2 = .005  $\mu F$  C3 = .1  $\mu F$

G = VIA to GND plane layer V = VIA to respective supply plane layer

Note: Each supply plane or strip should have a **ferrite bead and capacitors** All bypass caps = .1- $\mu f$  ceramic

<sup>\*</sup> For use with onboard video using 48 MHz for Dot Clock or connect to VDDQ3

### **Package Diagram**

#### 48-lead Shrunk Small Outline Package O48

Purchase of  $I^2$ C components from Cypress, or one of its sublicensed Associated Companies, conveys a license under the Philips  $I^2$ C Patent Rights to use these components in an  $I^2$ C system, provided that the system conforms to the  $I^2$ C Standard Specification as defined by Philips. Athlon and Duron are trademarks of Advanced Micro Devices, Inc. Dial-A-Frequency is a registered trademark of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.

# **Document History Page**

| Document Title: CY28372 SiS 746 AMD Athlon™/AMD Duron™ Clock Synthesizer Document Number: 38-07533 |         |            |                    |                         |  |  |

|----------------------------------------------------------------------------------------------------|---------|------------|--------------------|-------------------------|--|--|

| REV.                                                                                               | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change   |  |  |

| **                                                                                                 | 125162  | 04/25/03   | RGL                | New data sheet          |  |  |

| *A                                                                                                 | 266732  | See ECN    | RGL                | Added Lead-Free devices |  |  |