Instruments

**ISO1050**

SLLS983J - JUNE 2009 - REVISED SEPTEMBER 2019

# **ISO1050 Isolated CAN Transceiver**

### **Features**

- Meets the Requirements of ISO11898-2

- 5000-V<sub>RMS</sub> Isolation (ISO1050DW)

- 2500-V<sub>RMS</sub> Isolation (ISO1050DUB)

- Fail-Safe Outputs

- Low Loop Delay: 150 ns (Typical), 210 ns (Maximum)

- 50-kV/μs Typical Transient Immunity

- Bus-Fault Protection of -27 V to 40 V

- Driver (TXD) Dominant Time-out Function

- I/O Voltage Range Supports 3.3-V and 5-V Microprocessors

- VDE Approval per DIN VDE V 0884-11:2017-01 and DIN EN 61010-1

- UL 1577 Approved

- CSA Approved for IEC 60950-1, IEC 61010-1, IEC 60601-1 3rd Ed (Medical)

- TUV 5-KV<sub>RMS</sub> Reinforced Insulation Approval for EN/UL/CSA 60950-1 (ISO1050DW-Only)

- CQC Reinforced Insulation per GB4843.1-2011 (ISO1050DW-Only)

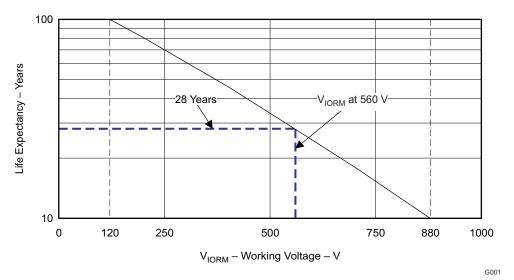

- Typical 25-Year Life at Rated Working Voltage (see Application Report SLLA197 and Life Expectancy vs Working Voltage)

# 2 Applications

- Industrial automation, control, sensors, and drive

- Building and climate control (HVAC) automation

- Security systems

- **Transportation**

- Medical

- Telecom

- CAN bus standards such as CANopen, DeviceNet, NMEA2000, ARINC825, ISO11783, CAN Kingdom, CANaerospace

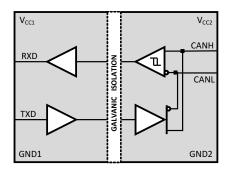

## 3 Description

The ISO1050 is a galvanically isolated CAN transceiver that meets the specifications of the ISO11898-2 standard. The device has the logic input and output buffers separated by a silicon oxide (SiO<sub>2</sub>) insulation barrier that provides galvanic isolation of up to 5000  $V_{RMS}$  for ISO1050DW and 2500  $V_{RMS}$  for ISO1050DUB. Used in conjunction with isolated power supplies, the device prevents noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry.

As a CAN transceiver, the device provides differential transmit capability to the bus and differential receive capability to a CAN controller at signaling rates up to 1 megabit per second (Mbps). The device is designed for operation in especially harsh environments, and it features cross-wire, overvoltage and loss of ground protection from -27 V to 40 V and overtemperature shutdown, as well as -12-V to 12-V common-mode range.

The ISO1050 is characterized for operation over the ambient temperature range of -55°C to 105°C.

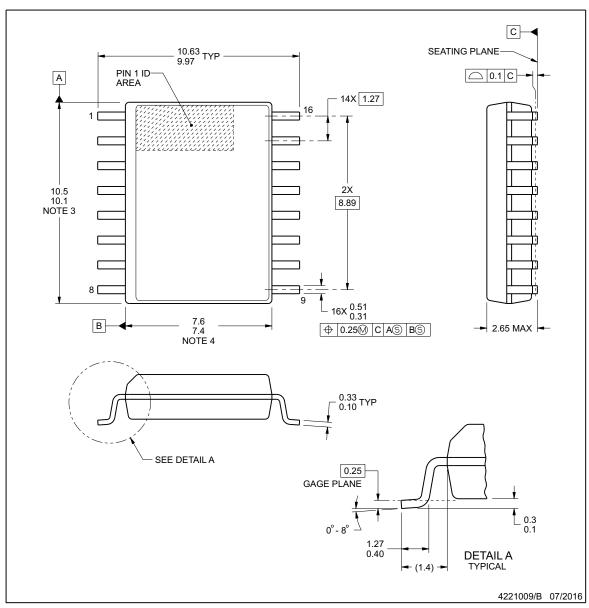

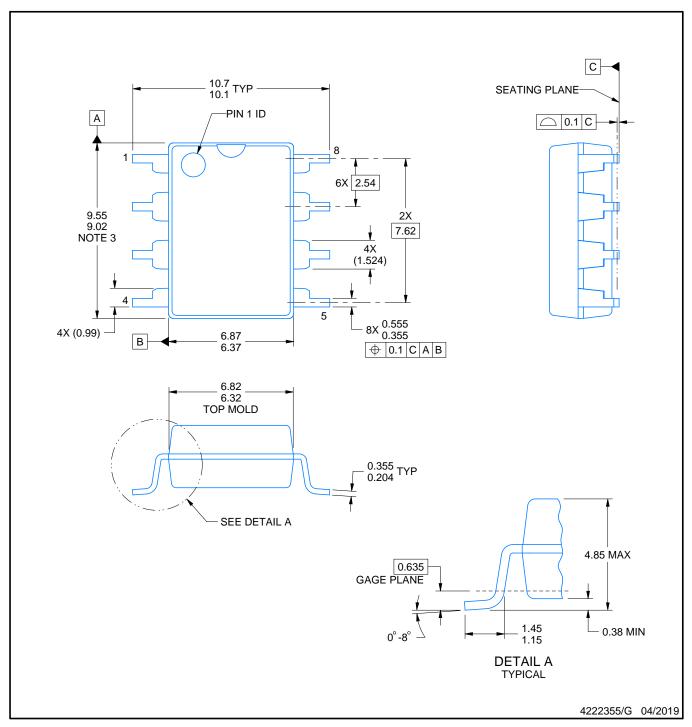

#### Device Information<sup>(1)</sup>

|   | PART NUMBER | PACKAGE   | BODY SIZE (NOM)    |  |  |

|---|-------------|-----------|--------------------|--|--|

|   | ISO1050     | SOP (8)   | 9.50 mm × 6.57 mm  |  |  |

| ' |             | SOIC (16) | 10.30 mm × 7.50 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

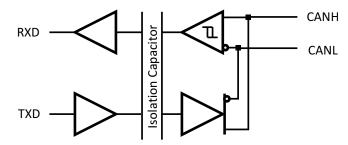

### Simplified Schematic

### **Table of Contents**

| 1 | Features 1                                     |    | 8.1 Overview                                     | 15              |

|---|------------------------------------------------|----|--------------------------------------------------|-----------------|

| 2 | Applications 1                                 |    | 8.2 Functional Block Diagram                     | 15              |

| 3 | Description 1                                  |    | 8.3 Feature Description                          | 15              |

| 4 | Revision History2                              |    | 8.4 Device Functional Modes                      | 20              |

| 5 | Pin Configuration and Functions5               | 9  | Application and Implementation                   | 22              |

| 6 | Specifications6                                |    | 9.1 Application Information                      | <mark>22</mark> |

| U | 6.1 Absolute Maximum Ratings                   |    | 9.2 Typical Application                          | 22              |

|   | 6.2 ESD Ratings                                | 10 | Power Supply Recommendations                     | 25              |

|   | 6.3 Recommended Operating Conditions           |    | 10.1 General Recommendations                     | 25              |

|   | 6.4 Thermal Information                        |    | 10.2 Power Supply Discharging                    | 25              |

|   | 6.5 Electrical Characteristics: Supply Current | 11 | Layout                                           | 25              |

|   | 6.6 Electrical Characteristics: Output Current |    | 11.1 Layout Guidelines                           |                 |

|   | 6.7 Electrical Characteristics: Briver         |    | 11.2 Layout Example                              |                 |

|   | 6.8 Switching Characteristics: Device          | 12 | Device and Documentation Support                 |                 |

|   | 6.9 Switching Characteristics: Driver          |    | 12.1 Documentation Support                       |                 |

|   | 6.10 Switching Characteristics: Receiver       |    | 12.2 Trademarks                                  |                 |

|   | 6.11 Typical Characteristics                   |    | 12.3 Electrostatic Discharge Caution             | <u>27</u>       |

| 7 | Parameter Measurement Information 10           |    | 12.4 Glossary                                    |                 |

| 8 | Detailed Description                           | 13 | Mechanical, Packaging, and Orderable Information | 27              |

### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI       | nanges from Revision I (September 2014) to Revision J                                                                                       | Page    |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|---------|

| •        | Changed VDE standard name From: DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 To: DIN VDE V 0884-11:2017-01 in Features                       | 1       |

| •        | Deleted 'Component Acceptance Notice 5 A' from CSA bullet in Features                                                                       | 1       |

| •        | Changed inverting output label From: CANH To: CANL in Figure 16                                                                             | 13      |

| •        | Changed VDE standard name From: DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 To: DIN VDE V 0884-11:2017-01 in Table 3                        | 16      |

| •        | Changed V <sub>ISO</sub> PARAMETER description From: 'ISO1050DUB - Double Protection' To: 'ISO1050DUB - Single Protection' in Table 3       | 16      |

| •        | Updated Regulatory Information in Table 6                                                                                                   | 17      |

| •        | Changed UL 1577 rating for ISO1050DUB From: '2500 V <sub>RMS</sub> Double Protection' To: '2500 V <sub>RMS</sub> Single Protection' Table 6 |         |

| •        | Deleted UL 1577 'Double Protection' rating of 3500 V <sub>RMS</sub> for ISO1050DW in Table 6                                                | 17      |

| •        | Added Power Supply Discharging section and SN6505 reference to Power Supply Recommendations                                                 | 25      |

| <u>.</u> | Added SN6505x data sheet link to 'Transformer Driver for Isolated Power Supplies' in Documentation Support sec                              | tion 27 |

| CI       | nanges from Revision H (June 2013) to Revision I                                                                                            | Page    |

| •        | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functions                             | al      |

### Changes from Revision G (March 2013) to Revision H

**Page**

......21

| Cł | nanges from Revision F (January 2013) to Revision G                                                               | Page |

|----|-------------------------------------------------------------------------------------------------------------------|------|

| •  | Clarified clearance and creepage measurement method in ISOLATOR CHARACTERISTICS                                   | 15   |

| •  | Clarified test methods for voltage ratings in INSULATION CHARACTERISTICS                                          | 16   |

| •  | Changed UL Single Protection Certification pending to Single Protection in REGULATORY INFORMATION                 |      |

|    | SECTION (certificate available)                                                                                   | 17   |

|    |                                                                                                                   |      |

| Cł | nanges from Revision E (December 2011) to Revision F                                                              | Page |

| •  | Deleted ISO1050L device                                                                                           | 1    |

| •  | Deleted ISO1050LDW from Features list                                                                             |      |

| •  | Deleted ISO1050LDW in first paragraph of DESCRIPTION                                                              | 1    |

| •  | Added the PIN FUNCTIONS section                                                                                   | 5    |

| •  | Added Note 1 to the DRIVER SWITCHING CHARACTERISTICS table                                                        | 8    |

| •  | Deleted ISO1050LDW from INSULATION CHARACTERISTICS                                                                | 16   |

| •  | Deleted ISO1050LDW from REGULATORY INFORMATION                                                                    | 17   |

| •  | Added the FUNCTIONAL DESCRIPTION section                                                                          | 17   |

| •  | Deleted ISO1050LDW from LIFE EXPECTANCY vs WORKING VOLTAGE                                                        | 21   |

| •  | Deleted 40V from the CANH and CANL input diagrams and output diagrams in the EQUIVALENT I/O SCHEMATICS            | 21   |

| •  | Changed the APPLICATION INFORMATION section                                                                       | 22   |

| •  | Changed the BUS LOADING, LENGHT AND NUMBER OF NODES section                                                       |      |

| •  | Added the CAN TERMINATION section                                                                                 |      |

|    |                                                                                                                   |      |

| Cł | nanges from Revision D (June 2011) to Revision E                                                                  | Page |

| •  | Added device ISO1050L                                                                                             | 1    |

| •  | Changed (DW Package) in the Features list to (ISO1050DW)                                                          | 1    |

| •  | Changed (DUB Package) in the Features list to (ISO1050DUB and ISO1050LDW)                                         | 1    |

| •  | Deleted IEC 60950-1 from the CSA Approvals Feature bullet                                                         | 1    |

| •  | From: IEC 60601-1 (Medical) and CSA Approvals Pending To: IEC 60601-1 (Medical) and CSA Approved                  |      |

| •  | Added Feature - 5 KVRMS Reinforced.                                                                               | 1    |

| •  | Changed DW Package to ISO105DW and DUB package to ISO1050DUB and ISO1050LDW in the first paragraph of DESCRIPTION |      |

| •  | Added Note 1 to the INSULATION CHARACTERISTICS table                                                              |      |

| •  | Changed V <sub>IORM</sub> From: 8-DUB Package to ISO1050DUB and ISO1050LDW                                        | 16   |

| •  | Changed V <sub>IORM</sub> From: 16-DW to ISO1050DW                                                                |      |

| •  | Changed the V <sub>ISO</sub> Isolation voltage per UL section of the INSULATION CHARACTERISTICS table             |      |

| •  | Changed the IEC 60664-1 Ratings Table                                                                             |      |

| •  | Changed the REGULATORY INFORMATION table                                                                          |      |

| •  | Changed in note (1) 3000 to 2500 and 6000 to 5000                                                                 |      |

| •  | Changed From: File Number: 220991 (Approval Pending) To: File Number: 220991                                      |      |

| •  | Changed in LIFE EXPECTANCY vs WORKING VOLTAGE (8-DUB PACKAGE TO: LIFE(ISO1050DW and ISO1050LDW)                   |      |

| Changes from Revision C (July 2010) to Revision D                                                                     | Page     |

|-----------------------------------------------------------------------------------------------------------------------|----------|

| <ul> <li>Changed the SUPPLY CURRENT table for I<sub>CC1</sub> 1st row From: Typ = 1 To: 1.8 and MAX = 2 To</li> </ul> | o: 2.8 7 |

| <ul> <li>Changed the SUPPLY CURRENT table for I<sub>CC1</sub> 2nd row From: Typ = 2 To: 2.8 and MAX = 3 T</li> </ul>  | o: 3.6 7 |

| Changed the REGULATORY INFORMATION table                                                                              | 17       |

| Changes from Revision B (June 2009) to Revision C                                                                     | Page     |

| Changed the IEC 60747-5-2 Features bullet From: DW package Approval Pending To: VDE ap and DW packages                |          |

| • Changed the Minimum Internal Gap value from 0.008 to 0.014 in the Isolator Characteristics ta                       | ble 15   |

| Changed V <sub>IORM</sub> Specification From: 1300 To: 1200 per VDE certification                                     | 16       |

| Changed V <sub>PR</sub> Specification From 2438 To: 2250                                                              | 16       |

| Added the Bus Loading paragraph to the Application Information section                                                | 22       |

| Changes from Revision A (Sept 2009) to Revision B                                                                     | Page     |

| Added information that IEC 60747-5-2 and IEC61010-1 have been approved                                                | 1        |

| Changed DW package from preview to production data                                                                    | 5        |

| Added Insulation Characteristics and IEC 60664-1 Ratings tables                                                       | 16       |

| Added IEC file number                                                                                                 | 17       |

| Changes from Original (June 2009) to Revision A                                                                       | Page     |

| Added Typical 25-Year Life at Rated Working Voltage to Features                                                       | 1        |

| Added LIFE EXPECTANCY vs WORKING VOLTAGE section                                                                      | 21       |

Submit Documentation Feedback

Copyright © 2009–2019, Texas Instruments Incorporated

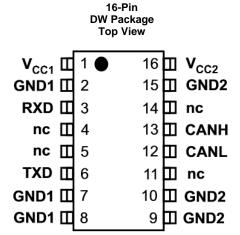

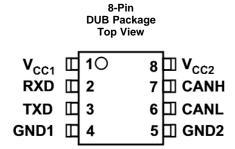

# 5 Pin Configuration and Functions

### **Pin Functions**

| PIN                                                 |    | TVDE                               | DESCRIPTION |                                                                              |  |  |  |

|-----------------------------------------------------|----|------------------------------------|-------------|------------------------------------------------------------------------------|--|--|--|

| NAME                                                |    |                                    | ITPE        | DESCRIPTION                                                                  |  |  |  |

| V <sub>CC1</sub>                                    | 1  | 1                                  | Supply      | Digital-side supply voltage (3 to 5.5 V)                                     |  |  |  |

| GND1                                                | 2  | _                                  | Ground      | Digital-side ground connection                                               |  |  |  |

| RXD                                                 | 3  | 2                                  | 0           | I receive data output (LOW for dominant and HIGH for recessive bus states)   |  |  |  |

| NC                                                  | 4  | _                                  | NC          | connect                                                                      |  |  |  |

| NC                                                  | 5  | _                                  | NC          | No connect                                                                   |  |  |  |

| TXD                                                 | 6  | 3                                  | I           | CAN transmit data input (LOW for dominant and HIGH for recessive bus states) |  |  |  |

| GND1                                                | 7  | 4                                  | Ground      | Digital-side ground connection                                               |  |  |  |

| GND1                                                | 8  | _                                  | Ground      | Digital-side ground connection                                               |  |  |  |

| GND2                                                | 9  | 5                                  | Ground      | Transceiver-side ground connection                                           |  |  |  |

| GND2                                                | 10 | _                                  | Ground      | Transceiver-side ground connection                                           |  |  |  |

| NC                                                  | 11 | _                                  | NC          | No connect                                                                   |  |  |  |

| CANL                                                | 12 | 6                                  | I/O         | Low-level CAN bus line                                                       |  |  |  |

| CANH                                                | 13 | 7                                  | I/O         | High-level CAN bus line                                                      |  |  |  |

| NC                                                  | 14 | _                                  | NC          | No connect                                                                   |  |  |  |

| GND2 15 — Ground Transceiver-side ground connection |    | Transceiver-side ground connection |             |                                                                              |  |  |  |

| V <sub>CC2</sub>                                    | 16 | 8                                  | Supply      | Transceiver-side supply voltage (5 V)                                        |  |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings (1)(2)

|                                        |                                          | MIN             | MAX                                   | UNIT |

|----------------------------------------|------------------------------------------|-----------------|---------------------------------------|------|

| V <sub>CC1</sub> , V <sub>CC2</sub>    | Supply voltage (3)                       | -0.5            | 6                                     | V    |

| $V_{I}$                                | Voltage input (TXD)                      | -0.5            | V <sub>CC1</sub> + 0.5 <sup>(4)</sup> | V    |

| V <sub>CANH</sub> or V <sub>CANL</sub> | Voltage at any bus terminal (CANH, CANL) | -27             | 40                                    | V    |

| I <sub>O</sub>                         | Receiver output current                  | -15             | 15                                    | mA   |

| $T_J$                                  | Junction temperature                     | <b>–</b> 55     | 150                                   | °C   |

| T <sub>stg</sub>                       | Storage temperature                      | <del>-</del> 65 | 150                                   | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) This isolator is suitable for isolation within the safety limiting data. Maintenance of the safety data must be ensured by means of protective circuitry.

- (3) All input and output logic voltage values are measured with respect to the GND1 logic side ground. Differential bus-side voltages are measured to the respective bus-side GND2 ground terminal.

- (4) Maximum voltage must not exceed 6 V.

## 6.2 ESD Ratings

|                    |                                                                                                                  |                                                                  | VALUE | UNIT |

|--------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|------|

|                    |                                                                                                                  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1) | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1500                                                            | V     |      |

| , ,                | diconargo                                                                                                        | Machine model, ANSI/ESDS5.2-1996, all pins                       | ±200  |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

|                                   |                                             |                                                                                                                                                           | MIN                | NOM | MAX  | UNIT    |  |

|-----------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|------|---------|--|

| V <sub>CC1</sub>                  | Supply voltage, controller side             |                                                                                                                                                           | 3                  |     | 5.5  | V       |  |

| $V_{CC2}$                         | Supply voltage, bus side                    |                                                                                                                                                           | 4.75               | 5   | 5.25 | V       |  |

| V <sub>I</sub> or V <sub>IC</sub> | Voltage at bus pins (separately or c        | common mode)                                                                                                                                              | -12 <sup>(1)</sup> |     | 12   | V       |  |

| $V_{IH}$                          | High-level input voltage                    | TXD                                                                                                                                                       | 2                  |     | 5.25 | V       |  |

| V <sub>IL</sub>                   | Low-level input voltage                     | TXD                                                                                                                                                       | 0                  |     | 0.8  | V       |  |

| V <sub>ID</sub>                   | Differential input voltage                  |                                                                                                                                                           |                    |     | 7    | V       |  |

|                                   | High lovel quitout gurrent                  | Driver                                                                                                                                                    | -70                |     |      | A       |  |

| Іон                               | High-level output current                   | Receiver                                                                                                                                                  | -4                 |     |      | mA      |  |

|                                   | Law law Law and a summer to                 | Driver                                                                                                                                                    |                    |     | 70   | ^       |  |

| l <sub>OL</sub>                   | Low-level output current                    | Receiver                                                                                                                                                  |                    |     | 4    | mA<br>1 |  |

| T <sub>A</sub>                    | Ambient Temperature                         |                                                                                                                                                           | <b>-</b> 55        |     | 105  | °C      |  |

| TJ                                | Junction temperature (see Thermal           | Information)                                                                                                                                              | -55                |     | 125  | °C      |  |

| P <sub>D</sub>                    | Total power dissipation                     |                                                                                                                                                           |                    |     | 200  |         |  |

| P <sub>D1</sub>                   | Power dissipation by Side-1                 | $V_{\text{CC1}}$ = 5.5V, $V_{\text{CC2}}$ = 5.25V, $T_{\text{A}}$ =105°C, $R_{\text{L}}$ = 60 $\Omega$ , TXD input is a 500kHz 50% duty-cycle square wave |                    |     | 25   | mW      |  |

| P <sub>D2</sub>                   | Power dissipation by Side-2                 | 1 1/D iliput is a 300ki iz 30 % duty-cycle squale wave                                                                                                    |                    |     | 175  |         |  |

| T <sub>j shutdown</sub>           | Thermal shutdown temperature <sup>(2)</sup> |                                                                                                                                                           |                    | 190 |      | °C      |  |

(1) The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

(2) Extended operation in thermal shutdown may affect device reliability.

### 6.4 Thermal Information

|                      |                                              | ISO10   | ISO1050 |       |  |  |

|----------------------|----------------------------------------------|---------|---------|-------|--|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | DW      | DUB     | UNIT  |  |  |

|                      |                                              | 16 PINS | 8 PINS  |       |  |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 76.0    | 73.3    |       |  |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 41      | 63.2    |       |  |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 47.7    | 43.0    | °C/W  |  |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 14.4    | 27.4    | 10/00 |  |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 38.2    | 42.7    |       |  |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | n/a     | n/a     |       |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

## 6.5 Electrical Characteristics: Supply Current

over recommended operating conditions (unless otherwise noted)

| PARAMETER        |                                 |                                                            | TEST CONDITIONS                                          | MIN TYP <sup>(1)</sup> | MAX | UNIT |

|------------------|---------------------------------|------------------------------------------------------------|----------------------------------------------------------|------------------------|-----|------|

|                  |                                 | $V_I = 0 \text{ V or } V_{CC1}$ , $V_{CC1} = 3.3 \text{V}$ | 1.8                                                      | 2.8                    | A   |      |

| ICC1             | V <sub>CC1</sub> Supply current |                                                            | $V_I = 0 \text{ V or } V_{CC1}$ , $V_{CC1} = 5 \text{V}$ | 2.3                    | 3.6 | mA   |

|                  | V Complete accompant            | Dominant                                                   | $V_I = 0 \text{ V}, 60-\Omega \text{ Load}$              | 52                     | 73  |      |

| I <sub>CC2</sub> | V <sub>CC2</sub> Supply current | Recessive                                                  | $V_I = V_{CC1}$                                          | 8                      | 12  | mA   |

<sup>(1)</sup> All typical values are at 25°C with  $V_{CC1} = V_{CC2} = 5 \text{ V}$ .

### 6.6 Electrical Characteristics: Driver

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                        |         | TEST CONDITIONS                                                                          | MIN        | TYP  | MAX   | UNIT     |

|---------------------|--------------------------------------------------|---------|------------------------------------------------------------------------------------------|------------|------|-------|----------|

| \/                  | Pure sustant valtage (Deminent)                  | CANH    | See Figure 7 and Figure 8 V OV B 60 O                                                    | 2.9        | 3.5  | 4.5   | V        |

| $V_{O(D)}$          | Bus output voltage (Dominant)                    | CANL    | See Figure 7 and Figure 8, $V_I = 0 \text{ V}$ , $R_L = 60 \Omega$                       | 0.8        | 1.2  | 1.5   | V        |

| $V_{O(R)}$          | Bus output voltage (Recessive)                   |         | See Figure 7 and Figure 8, $V_I = 2 V$ , $R_L = 60 \Omega$                               | 2          | 2.3  | 3     | V        |

| V                   | Differential output voltage (Deminent            | `       | See Figure 7, Figure 8 and Figure 9, $V_I$ = 0 $V$ , $R_L$ = 60 $\Omega$                 | 1.5        |      | 3     | V        |

| V <sub>OD(D)</sub>  | Differential output voltage (Dominant)           |         | See Figure 7, Figure 8, and Figure 9 $V_I$ = 0 $V$ , $R_L$ = 45 $\Omega$ , Vcc > 4.8 $V$ | 1.4        |      | 3     | V        |

| V                   | Differential output valtege (Decesive            | -\      | See Figure 7 and Figure 8, $V_I = 3 \text{ V}$ , $R_L = 60 \Omega$                       | -0.12      |      | 0.012 | <b>V</b> |

| $V_{OD(R)}$         | Differential output voltage (Recessive)          |         | V <sub>I</sub> = 3 V, No Load                                                            | -0.5       |      | 0.05  | V        |

| V <sub>OC(D)</sub>  | Common-mode output voltage (Dom                  | inant)  | See Figure 44                                                                            | 2          | 2.3  | 3     | V        |

| V <sub>OC(pp)</sub> | Peak-to-peak common-mode output                  | voltage | See Figure 14                                                                            |            | 0.3  |       | V        |

| I <sub>IH</sub>     | High-level input current, TXD input              |         | V <sub>I</sub> at 2 V                                                                    |            |      | 5     | μΑ       |

| I <sub>IL</sub>     | Low-level input current, TXD input               |         | V <sub>I</sub> at 0.8 V                                                                  | <b>-</b> 5 |      |       | μΑ       |

| I <sub>O(off)</sub> | Power-off TXD leakage current                    |         | V <sub>CC1</sub> , V <sub>CC2</sub> at 0 V, TXD at 5 V                                   |            |      | 10    | μΑ       |

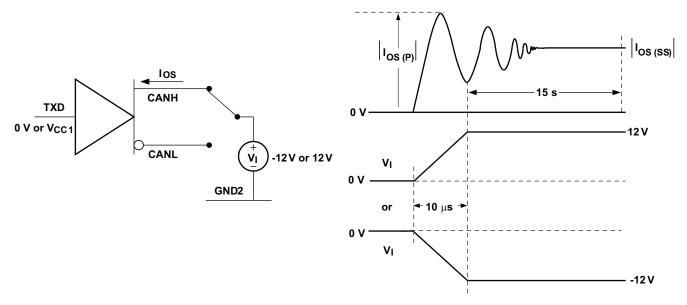

|                     |                                                  |         | See Figure 17, V <sub>CANH</sub> = -12 V, CANL Open                                      | -105       | -72  |       |          |

|                     | Chant circuit at a dr. at at a critical transfer |         | See Figure 17, V <sub>CANH</sub> = 12 V, CANL Open                                       |            | 0.36 | 1     | A        |

| I <sub>OS(ss)</sub> | Short-circuit steady-state output curr           | ent     | See Figure 17, V <sub>CANL</sub> =–12 V, CANH Open                                       | -1         | -0.5 |       | mA       |

|                     |                                                  |         | See Figure 17, V <sub>CANL</sub> = 12 V, CANH Open                                       |            | 71   | 105   |          |

| Co                  | Output capacitance                               |         | See receiver input capacitance                                                           |            |      |       |          |

| CMTI                | Common-mode transient immunity                   |         | See Figure 19, V <sub>I</sub> = V <sub>CC</sub> or 0 V                                   | 25         | 50   |       | kV/μs    |

### 6.7 Electrical Characteristics: Receiver

over recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                                                                                 | TEST CONDITIONS                                        | MIN                   | TYP <sup>(1)</sup> | MAX | UNIT  |

|-------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------|--------------------|-----|-------|

| $V_{IT+}$         | Positive-going bus input threshold voltage                                                | See Table 1                                            |                       | 750                | 900 | mV    |

| $V_{IT-}$         | Negative-going bus input threshold voltage                                                | See Table 1                                            | 500                   | 650                |     | mV    |

| V <sub>hys</sub>  | Hysteresis voltage (V <sub>IT+</sub> – V <sub>IT-</sub> )                                 |                                                        |                       | 150                |     | mV    |

| V                 | High-level output voltage with Vcc = 5 V                                                  | I <sub>OH</sub> = -4 mA, See Figure 12                 | V <sub>CC</sub> - 0.8 | 4.6                |     | V     |

| V <sub>OH</sub>   | nigii-level output voltage with vcc = 5 v                                                 | $I_{OH} = -20 \mu A$ , See Figure 12                   | V <sub>CC</sub> - 0.1 | 5                  |     | V     |

| \/                | High level output voltage with Voot - 2.2 V                                               | I <sub>OL</sub> = 4 mA, See Figure 12                  | V <sub>CC</sub> - 0.8 | 3.1                |     | V     |

| V <sub>OH</sub>   | High-level output voltage with Vcc1 = 3.3 V                                               | $I_{OL}$ = 20 $\mu$ A, See Figure 12                   | V <sub>CC</sub> - 0.1 | 3.3                |     | V     |

| .,                | Lave lavel and only of the ma                                                             | I <sub>OL</sub> = 4 mA, See Figure 12                  |                       | 0.2                | 0.4 | V     |

| V <sub>OL</sub>   | Low-level output voltage                                                                  | I <sub>OL</sub> = 20 μA, See Figure 12                 |                       | 0                  | 0.1 | V     |

| C <sub>I</sub>    | Input capacitance to ground, (CANH or CANL)                                               | TXD at 3 V, $V_1 = 0.4 \sin (4E6\pi t) + 2.5 V$        |                       | 6                  |     | рF    |

| $C_{ID}$          | Differential input capacitance                                                            | TXD at 3 V, $V_1 = 0.4 \sin (4E6\pi t)$                |                       | 3                  |     | рF    |

| $R_{\text{ID}}$   | Differential input resistance                                                             | TXD at 3 V                                             | 30                    |                    | 80  | kΩ    |

| R <sub>IN</sub>   | Input resistance (CANH or CANL)                                                           | TXD at 3 V                                             | 15                    | 30                 | 40  | kΩ    |

| R <sub>I(m)</sub> | Input resistance matching (1 – [R <sub>IN (CANH)</sub> / R <sub>IN (CANL)</sub> ]) × 100% | V <sub>CANH</sub> = V <sub>CANL</sub>                  | -3%                   | 0%                 | 3%  |       |

| CMTI              | Common-mode transient immunity                                                            | V <sub>I</sub> = V <sub>CC</sub> or 0 V, See Figure 19 | 25                    | 50                 |     | kV/μs |

<sup>(1)</sup> All typical values are at 25°C with  $V_{CC1} = V_{CC2} = 5 \text{ V}$ .

### 6.8 Switching Characteristics: Device

over recommended operating conditions (unless otherwise noted)

| PARAMETER          |                                                                          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>loop1</sub> | Total loop delay, driver input to receiver output, Recessive to Dominant | See Figure 15   | 112 | 150 | 210 | ns   |

| t <sub>loop2</sub> | Total loop delay, driver input to receiver output, Dominant to Recessive | See Figure 15   | 112 | 150 | 210 | ns   |

## 6.9 Switching Characteristics: Driver

over recommended operating conditions (unless otherwise noted)

|                                     | PARAMETER                                            | TEST CONDITIONS                         | MIN | TYP | MAX | UNIT |

|-------------------------------------|------------------------------------------------------|-----------------------------------------|-----|-----|-----|------|

| t <sub>PLH</sub>                    | Propagation delay time, recessive-to-dominant output |                                         | 31  | 74  | 110 |      |

| t <sub>PHL</sub>                    | Propagation delay time, dominant-to-recessive output | Coo Figure 40                           | 25  | 44  | 75  | 20   |

| t <sub>r</sub>                      | Differential output signal rise time                 |                                         |     |     | 50  | ns   |

| t <sub>f</sub>                      | Differential output signal fall time                 |                                         |     | 20  | 50  |      |

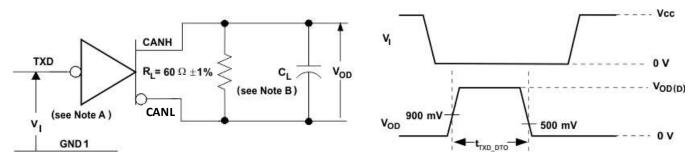

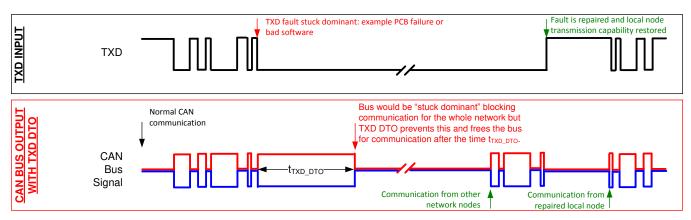

| t <sub>TXD_DTO</sub> <sup>(1)</sup> | Dominant time-out                                    | ↓ C <sub>L</sub> =100 pF, See Figure 16 | 300 | 450 | 700 | μS   |

(1) The TXD dominant time out (t<sub>TXD\_DTO</sub>) disables the driver of the transceiver once the TXD has been dominant longer than (t<sub>TXD\_DTO</sub>) which releases the bus lines to recessive preventing a local failure from locking the bus dominant. The driver may only transmit dominant again after TXD has been returned HIGH (recessive). While this protects the bus from local faults locking the bus dominant it limits the minimum data rate possible. The CAN protocol allows a maximum of eleven successive dominant bits (on TXD) for the worst case where five successive dominant bits are followed immediately by an error frame. This along with the (t<sub>TXD\_DTO</sub>) minimum limits the minimum bit rate. The minimum bit rate may be calculated by: Minimum Bit Rate = 11/ (t<sub>TXD\_DTO</sub>) = 11 bits / 300 µs = 37 kbps.

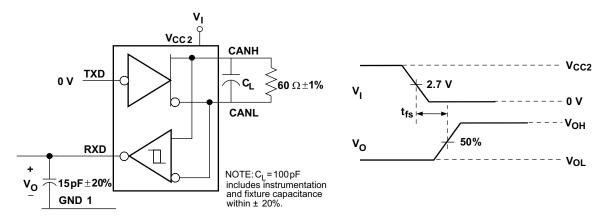

# 6.10 Switching Characteristics: Receiver

over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                                            | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|------------------|------------------------------------------------------|----------------------------|-----|-----|-----|------|

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output     |                            | 66  | 90  | 130 |      |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output     | TVD at 2 V. San Figure 42  | 51  | 80  | 105 | 20   |

| t <sub>r</sub>   | Output signal rise time  TXD at 3 V, See Figure 12   |                            |     | 3   | 6   | ns   |

| t <sub>f</sub>   | Output signal fall time                              |                            |     | 3   | 6   |      |

| t <sub>fs</sub>  | Fail-Safe output delay time from bus-side power loss | VCC1 at 5 V, See Figure 18 |     | 6   |     | μS   |

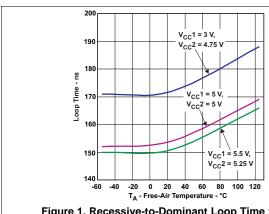

# 6.11 Typical Characteristics

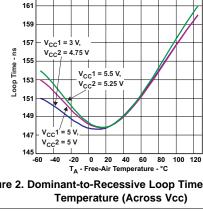

Figure 1. Recessive-to-Dominant Loop Time vs Free-Air Temperature (Across Vcc)

Figure 2. Dominant-to-Recessive Loop Time vs Free-Air

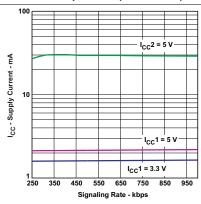

Figure 3. Supply Current (RMS) vs Signaling Rate (kbps)

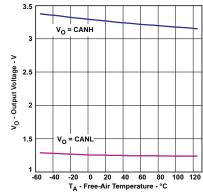

Figure 4. Driver Output Voltage vs Free-Air Temperature

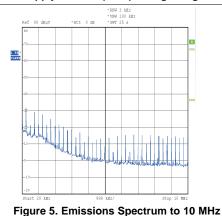

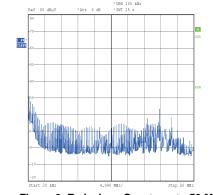

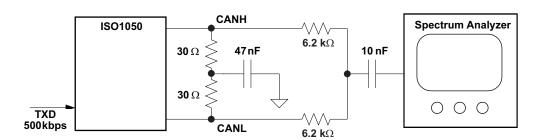

Figure 6. Emissions Spectrum to 50 MHz

Copyright © 2009-2019, Texas Instruments Incorporated

### 7 Parameter Measurement Information

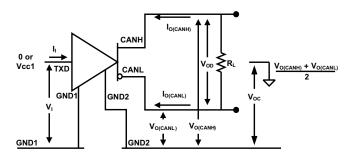

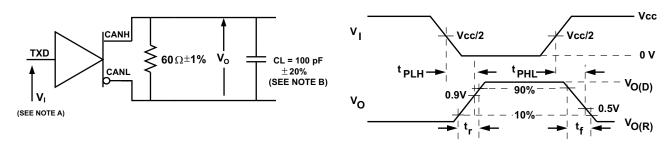

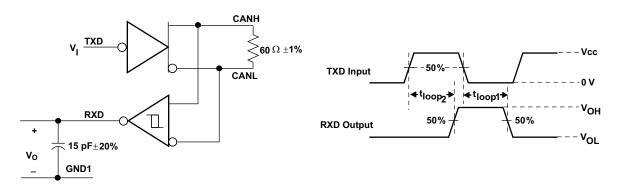

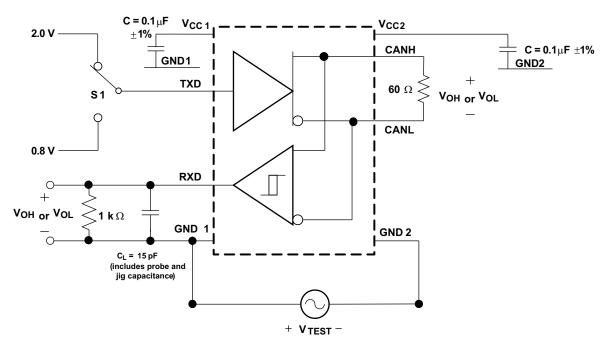

Figure 7. Driver Voltage, Current and Test Definitions

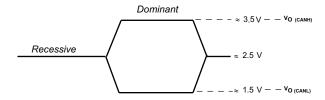

Figure 8. Bus Logic State Voltage Definitions

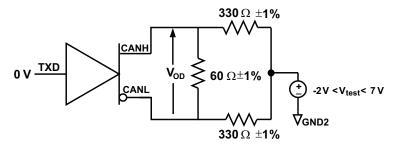

Figure 9. Driver VoD With Common-Mode Loading Test Circuit

- A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  125 kHz, 50% duty cycle,  $t_f \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50 \Omega$ .

- B.  $C_L$  includes instrumentation and fixture capacitance within  $\pm 20\%$ .

Figure 10. Driver Test Circuit and Voltage Waveforms

# **Parameter Measurement Information (continued)**

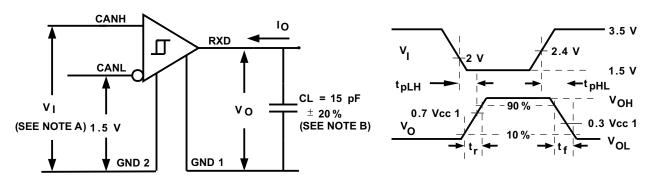

Figure 11. Receiver Voltage and Current Definitions

- A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  125 kHz, 50% duty cycle,  $t_r \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50 \Omega$ .

- B.  $C_L$  includes instrumentation and fixture capacitance within  $\pm 20\%$ .

Figure 12. Receiver Test Circuit and Voltage Waveforms

**Table 1. Differential Input Voltage Threshold Test**

|                   |                   | OUTPUT          |   |                 |  |

|-------------------|-------------------|-----------------|---|-----------------|--|

| V <sub>CANH</sub> | V <sub>CANL</sub> | V <sub>ID</sub> | R |                 |  |

| –11.1 V           | –12 V             | 900 mV          | L |                 |  |

| 12 V              | 11.1 V            | 900 mV          | L | V               |  |

| −6 V              | -12 V             | 6 V             | L | V <sub>OL</sub> |  |

| 12 V              | 6 V               | 6 V             | L |                 |  |

| –11.5 V           | -12 V             | 500 mV          | Н |                 |  |

| 12 V              | 11.5 V            | 500 mV          | Н |                 |  |

| –12 V             | -6 V              | -6 V            | Н | V <sub>OH</sub> |  |

| 6 V               | 12 V              | -6 V            | Н |                 |  |

| Open              | Open              | X               | Н |                 |  |

Copyright © 2009–2019, Texas Instruments Incorporated

The waveforms of the applied transients are in accordance with ISO 7637 part 1, test pulses 1, 2, 3a, and 3b.

Figure 13. Transient Overvoltage Test Circuit

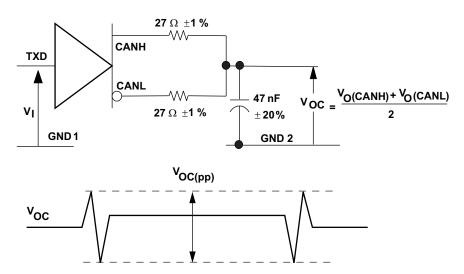

Figure 14. Peak-to-Peak Output Voltage Test Circuit and Waveform

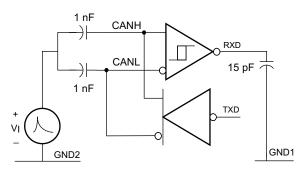

Figure 15. t<sub>LOOP</sub> Test Circuit and Voltage Waveforms

- A. The input pulse is supplied by a generator having the following characteristics:  $t_r \le 6$  ns,  $t_f \le 6$  ns,  $t_O = 50$   $\Omega$ .

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within ±20%.

Figure 16. Dominant Time-out Test Circuit and Voltage Waveforms

Figure 17. Driver Short-Circuit Current Test Circuit and Waveforms

Figure 18. Fail-Safe Delay Time Test Circuit and Voltage Waveforms

Copyright © 2009–2019, Texas Instruments Incorporated

Figure 19. Common-Mode Transient Immunity Test Circuit

Figure 20. Electromagnetic Emissions Measurement Setup

# 8 Detailed Description

#### 8.1 Overview

The ISO1050 is a digitally isolated CAN transceiver with a typical transient immunity of 50 kV/µs. The device can operate from 3.3-V supply on side 1 and 5-V supply on side 2. This is of particular advantage for applications operating in harsh industrial environments because the 3.3 V on side 1 enables the connection to low-volt microcontrollers for power preservation, whereas the 5 V on side 2 maintains a high signal-to-noise ratio of the bus signals.

### 8.2 Functional Block Diagram

# 8.3 Feature Description

Table 2. Isolator Characteristics (1)(2)

|                 | PARAMETER                                                                                                                                            | TEST CONDITIONS                                                                                     |        | MIN  | TYP               | MAX | UNIT |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------|------|-------------------|-----|------|

| L(I01)          | Minimum air gap (Clearance)                                                                                                                          | Shortest pin-to-pin distance through air, per JEDEC package dimensions                              | DUB-8  | 6.1  |                   |     | mm   |

| L(102)          | Minimum external tracking (Creepage)                                                                                                                 | Shortest pin-to-pin distance across the package surface, per JEDEC package dimensions               | DOB-6  | 6.8  |                   |     | mm   |

| L(I01)          | Minimum air gap (Clearance)                                                                                                                          | Shortest pin-to-pin distance through air, per JEDEC package dimensions                              | DW-16  | 8.34 |                   |     | mm   |

| L(102)          | Minimum external tracking (Creepage)                                                                                                                 | Shortest pin-to-pin distance across the package surface, per JEDEC package dimensions               | DVV-16 | 8.10 |                   |     | mm   |

|                 | Minimum Internal Gap (Internal Clearance)                                                                                                            | Distance through the insulation                                                                     |        |      |                   |     | mm   |

| R <sub>IO</sub> | Input to output, $V_{IO} = 500 \text{ V}$ , all pins on each side of the barrier tied together creating a two-pin device, $T_A = 25^{\circ}\text{C}$ |                                                                                                     |        |      | >10 <sup>12</sup> |     | Ω    |

|                 |                                                                                                                                                      | Input to output, $V_{IO} = 500 \text{ V}$ , $100^{\circ}\text{C} \leq T_{A} \leq T_{A} \text{ max}$ |        |      | >10 <sup>11</sup> |     | Ω    |

| C <sub>IO</sub> | Barrier capacitance                                                                                                                                  | $V_1 = 0.4 \sin (4E6\pi t)$                                                                         |        |      | 1.9               |     | pF   |

| C <sub>I</sub>  | Input capacitance to ground                                                                                                                          | $V_1 = 0.4 \sin (4E6\pi t)$                                                                         |        |      | 1.3               |     | pF   |

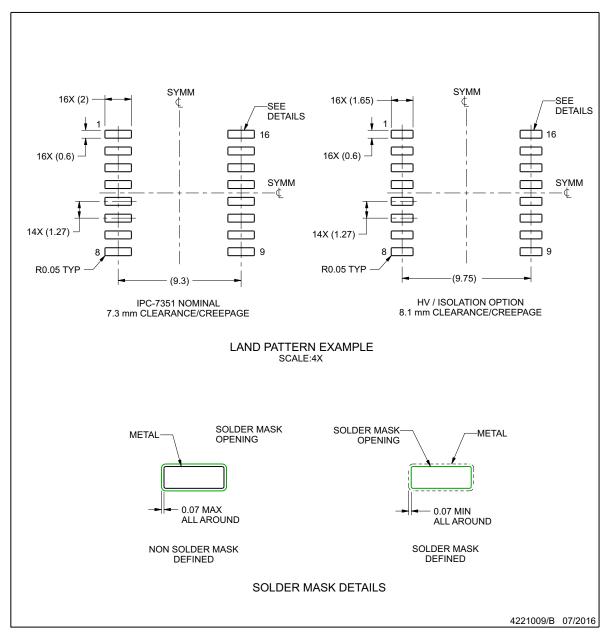

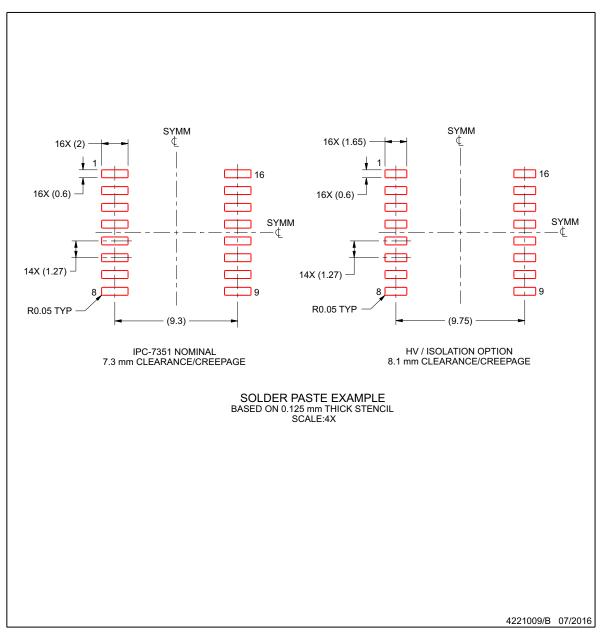

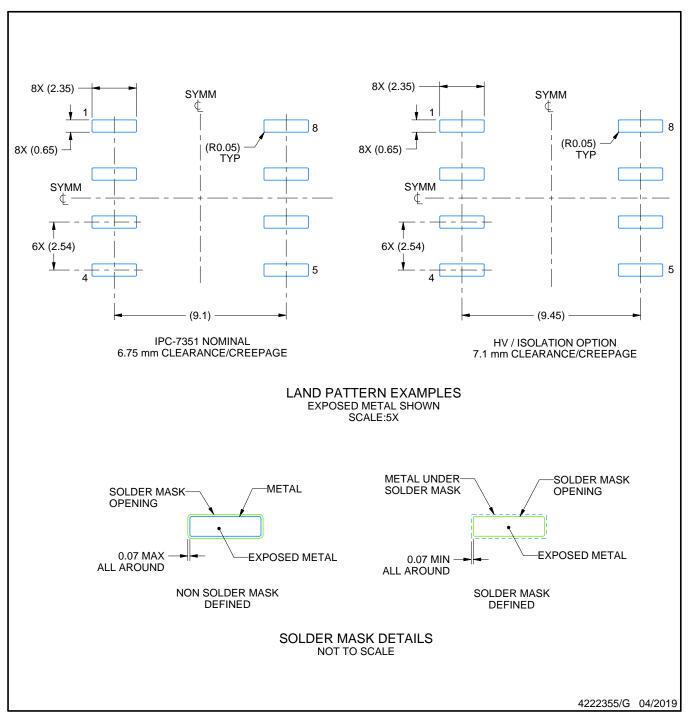

<sup>(1)</sup> Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit-board do not reduce this distance.

<sup>(2)</sup> Creepage and clearance on a printed-circuit-board become equal according to the measurement techniques shown in the Isolation Glossary. Techniques such as inserting grooves and/or ribs on a printed-circuit-board are used to help increase these specifications.

#### **Table 3. Insulation Characteristics**

|                   | PARAME                                    | TER                            | TEST CONDITIONS                                      | SPECIFICATION     | UNIT   |

|-------------------|-------------------------------------------|--------------------------------|------------------------------------------------------|-------------------|--------|

|                   | Maximum working insulation                |                                |                                                      | 560               |        |

| V <sub>IORM</sub> | voltage per DIN VDE V 0884-<br>11:2017-01 | ISO1050DW                      |                                                      | 1200              | Vpeak  |

|                   | Input to output test voltage per          | ISO1050DUB                     | V <sub>P R</sub> = 1.875 x V <sub>IORM</sub> , t = 1 | 1050              |        |

| $V_{PR}$          | DIN VDE V 0884-11:2017-01                 | ISO1050DW                      | sec (100% production) Partial discharge < 5 pC       | 2250              | Vpeak  |

| V                 | Transient overvoltage per DIN t = 60      |                                | t = 60 sec (qualification)                           | 4000              | Vacals |

| $V_{IOTM}$        | VDE V 0884-11:2017-01                     |                                | t = 1 sec (100% production)                          | 4000              | Vpeak  |

|                   |                                           | ICO4050DLID Circle Dretestion  | t = 60 sec (qualification)                           | 2500              | \/     |

| .,                | laslation valtage was III. 4577           | ISO1050DUB - Single Protection | t = 1 sec (100% production)                          | 3000              | Vrms   |

| V <sub>ISO</sub>  | Isolation voltage per UL 1577             | ICO4050DW Circle Dretestics    | t = 60 sec (qualification)                           | 4243              | \/     |

|                   |                                           | ISO1050DW - Single Protection  | t = 1 sec (100% production)                          | 5092              | Vrms   |

| $R_S$             | Isolation resistance                      |                                | $V_{IO}$ = 500 V at $T_S$                            | > 10 <sup>9</sup> | Ω      |

|                   | Pollution Degree                          |                                |                                                      | 2                 |        |

### Table 4. IEC 60664-1 Ratings

| PARAMETER TEST CONDITIONS   |                                                 | SPECIFICATION |

|-----------------------------|-------------------------------------------------|---------------|

| Basic isolation group       | sic isolation group Material group              |               |

|                             | Rated mains voltage ≤ 150 Vrms                  | I–IV          |

|                             | Rated mains voltage ≤ 300 Vrms                  | I–III         |

| Installation classification | Rated mains voltage ≤ 400 Vrms                  | I–II          |

|                             | Rated mains voltage ≤ 600 Vrms (ISO1050DW only) | I-II          |

|                             | Rated mains voltage ≤ 848 Vrms (ISO1050DW only) | I             |

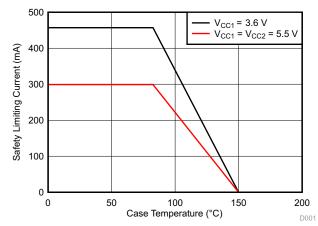

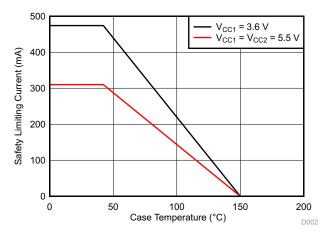

# Table 5. IEC Safety Limiting Values<sup>(1)</sup>

|       | PARAMETER TEST CONDITIONS               |                                                                                                 | MIN                                                                                             | TYP | MAX | UNIT |    |

|-------|-----------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|------|----|

|       | DUB-8                                   | $\theta_{JA} = 73.3 \text{ °C/W}, V_I = 5.5 \text{ V}, T_J = 150 \text{°C}, T_A = 25 \text{°C}$ |                                                                                                 |     | 310 | m ^  |    |

|       |                                         | DOP-0                                                                                           | $\theta_{JA} = 73.3 \text{ °C/W}, V_I = 3.6 \text{ V}, T_J = 150 \text{°C}, T_A = 25 \text{°C}$ |     |     | 474  | mA |

| IS    | Safety input, output, or supply current |                                                                                                 | $\theta_{JA} = 76 \text{ °C/W}, V_I = 5.5 \text{ V}, T_J = 150 \text{ °C}, T_A = 25 \text{ °C}$ |     |     | 299  | A  |

|       |                                         | DW-16                                                                                           | $\theta_{JA} = 76 \text{ °C/W}, V_I = 3.6 \text{ V}, T_J = 150 \text{ °C}, T_A = 25 \text{ °C}$ |     |     | 457  | mA |

| $T_S$ | Maximum case temperature                |                                                                                                 |                                                                                                 |     |     | 150  | ô  |

<sup>(1)</sup> Safety limiting intends to prevent potential damage to the isolation barrier upon failure of input or output circuitry. A failure of the I/O can allow low resistance to ground or the supply and, without current limiting dissipate sufficient power to overheat the die and damage the isolation barrier potentially leading to secondary system failures.

The safety-limiting constraint is the absolute maximum junction temperature specified in the absolute maximum ratings table. The power dissipation and junction-to-air thermal impedance of the device installed in the application hardware determines the junction temperature. The assured junction-to-air thermal resistance in *Thermal Information* is that of a device installed on a High-K Test Board for Leaded Surface Mount Packages. The power is the recommended maximum input voltage times the current. The junction temperature is then the ambient temperature plus the power times the junction-to-air thermal resistance.

Product Folder Links: ISO1050

Figure 21. DUB-8  $\theta_{\text{JC}}$  Thermal Derating Curve per VDE

Figure 22. DW-16  $\theta_{JC}$  Thermal Derating Curve per VDF

**Table 6. Regulatory Information**

| VDE                                                                                                                                                                                             | TUV                                                                                                                                                                                                                                                                                                                                                                                   | CSA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UL                                                                                                              | CQC                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Certified according to DIN<br>VDE V 0884-11:2017-01 &<br>DIN EN 61010-1                                                                                                                         | Certified according to EN/UL/CSA 60950-1                                                                                                                                                                                                                                                                                                                                              | Certified according to IEC 60950-<br>1, IEC 62368-1, IEC 61010-1 and<br>IEC 60601-1                                                                                                                                                                                                                                                                                                                                                                                                                            | Recognized under UL<br>1577 Component<br>Recognition Program <sup>(1)</sup>                                     | Certified according to GB4943.1-2011                                                                                |

| Basic Insulation Transient Overvoltage, 4000 V <sub>PK</sub> Surge Voltage, 4000 V <sub>PK</sub> Maximum Working Voltage, 1200 V <sub>PK</sub> (ISO1050DW) and 560 V <sub>PK</sub> (ISO1050DUB) | ISO1050DW:  5000 V <sub>RMS</sub> Reinforced Insulation, 400 V <sub>RMS</sub> maximum working voltage 5000 V <sub>RMS</sub> Basic Insulation, 600 V <sub>RMS</sub> maximum working voltage ISO1050DUB: 2500 V <sub>RMS</sub> Reinforced Insulation, 400 V <sub>RMS</sub> maximum working voltage 2500 V <sub>RMS</sub> Basic Insulation, 600 V <sub>RMS</sub> maximum working voltage | ISO1050DW:  5000 V <sub>RMS</sub> Reinforced Insulation 2 Means of Patient Protection at 225 V <sub>RMS</sub> per IEC 60601-1 Ed.3+A1 Working voltage of 380 V <sub>RMS</sub> per IEC 60950-1 2nd Ed.+A1+A2 and IEC 62368-1:2014 Working voltage of 300 V <sub>RMS</sub> per IEC 61010-1 3rd Ed. ISO1050DUB: 2500 V <sub>RMS</sub> Basic Insulation Working voltage of 700 V <sub>RMS</sub> per IEC 60950-1 2nd Ed.+A1+A2 Working voltage of 600 V <sub>RMS</sub> per IEC 61010-1 3rd Ed. and IEC 62368-1:2014 | ISO1050DUB: 2500 V <sub>RMS</sub><br>Single Protection<br>ISO1050DW: 4243 V <sub>RMS</sub><br>Single Protection | ISO1050DW: Reinforced Insulation, Altitude ≤ 5000 m, Tropical Climate, 250 V <sub>RMS</sub> maximum working voltage |

| Certificate number: 40047657                                                                                                                                                                    | Client ID number: 77311                                                                                                                                                                                                                                                                                                                                                               | Master contract number: 220991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | File number: E181974                                                                                            | Certificate number:<br>CQC14001109541                                                                               |

<sup>(1)</sup> Production tested ≥ 3000 V<sub>RMS</sub> (ISO1050DUB) and 5092 V<sub>RMS</sub> (ISO1050DW) for 1 second in accordance with UL 1577.

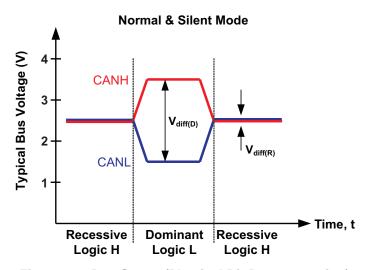

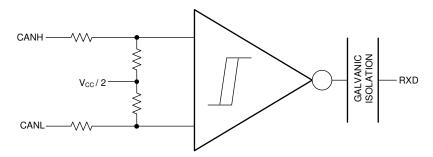

### 8.3.1 CAN Bus States

The CAN bus has two states during operation: dominant and recessive. A dominant bus state, equivalent to logic low, is when the bus is driven differentially by a driver. A recessive bus state is when the bus is biased to a common mode of  $V_{CC}$  / 2 through the high-resistance internal input resistors of the receiver, equivalent to a logic high. The host microprocessor of the CAN node will use the TXD pin to drive the bus and will receive data from the bus on the RXD pin. See Figure 23 and Figure 24.

Figure 23. Bus States (Physical Bit Representation)

Figure 24. Simplified Recessive Common Mode Bias and Receiver

#### 8.3.2 Digital Inputs and Outputs

### TXD (Input) and RXD (Output):

$V_{CC1}$  for the isolated digital input and output side of the device maybe supplied by a 3.3-V or 5-V supply and thus the digital inputs and outputs are 3.3-V and 5-V compatible.

#### NOTE

TXD is very weakly internally pulled up to  $V_{\text{CC1}}$ . An external pullup resistor should be used to make sure that TXD is biased to recessive (high) level to avoid issues on the bus if the microprocessor doesn't control the pin and TXD floats. TXD pullup strength and CAN bit timing require special consideration when the device is used with an open-drain TXD output on the CAN controller of the microprocessor. An adequate external pullup resistor must be used to ensure that the TXD output of the microprocessor maintains adequate bit timing input to the input on the transceiver.

#### 8.3.3 Protection Features

### 8.3.3.1 TXD Dominant Time-Out (DTO)

TXD DTO circuit prevents the local node from blocking network communication in the event of a hardware or software failure where TXD is held dominant longer than the time-out period  $t_{TXD\_DTO}$ . The TXD DTO circuit timer starts on a falling edge on TXD. The TXD DTO circuit disables the CAN bus driver if no rising edge is seen before the time-out period expires. This frees the bus for communication between other nodes on the network. The CAN driver is re-activated when a recessive signal is seen on the TXD pin, thus clearing the TXD DTO condition. The receiver and RXD pin still reflect the CAN bus, and the bus pins are biased to recessive level during a TXD dominant time-out.

#### NOTE

The minimum dominant TXD time allowed by the TXD DTO circuit limits the minimum possible transmitted data rate of the device. The CAN protocol allows a maximum of eleven successive dominant bits (on TXD) for the worst case, where five successive dominant bits are followed immediately by an error frame. This, along with the  $t_{TXD\_DTO}$  minimum, limits the minimum data rate. Calculate the minimum transmitted data rate by: Minimum Data Rate = 11 /  $t_{TXD\_DTO}$ .

Figure 25. Example Timing Diagram for Devices With TXD DTO

#### 8.3.3.2 Thermal Shutdown

If the junction temperature of the device exceeds the thermal shut down threshold the device turns off the CAN driver circuits thus blocking the TXD to bus transmission path. The shutdown condition is cleared when the junction temperature drops below the thermal shutdown temperature of the device. If the fault condition is still present, the temperature may rise again and the device would enter thermal shut down again. Prolonged operation with thermal shutdown conditions may affect device reliability.

### NOTE

During thermal shutdown the CAN bus drivers turn off; thus no transmission is possible from TXD to the bus. The CAN bus pins are biased to recessive level during a thermal shutdown, and the receiver to RXD path remains operational.

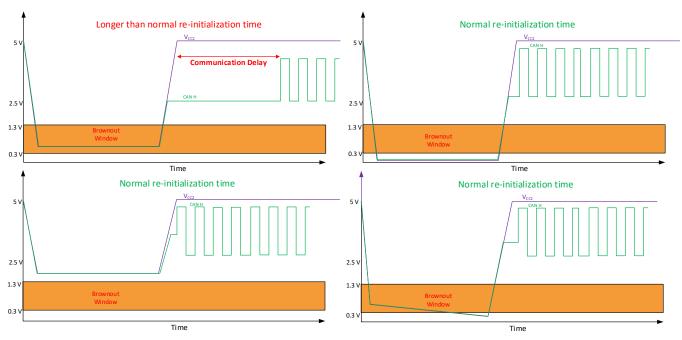

#### 8.3.3.3 Undervoltage Lockout and Fail-Safe

The supply pins have undervoltage detection that places the device in protected or fail-safe mode. This protects the bus during an undervoltage event on  $V_{CC1}$  or  $V_{CC2}$  supply pins. If the bus-side power supply  $V_{CC2}$  is lower than about 2.7 V, the power shutdown circuits in the ISO1050 will disable the transceiver to prevent false transmissions due to an unstable supply. If  $V_{CC1}$  is still active when this occurs, the receiver output (RXD) will go to a fail-safe HIGH (recessive) value in about 6 microseconds.

Table 7. Undervoltage Lockout and Fail-Safe

| V <sub>CC</sub> 1 | V <sub>CC</sub> 2 | DEVICE STATE | BUS OUTPUT               | RXD                        |

|-------------------|-------------------|--------------|--------------------------|----------------------------|

| GOOD              | GOOD              | Functional   | Per Device State and TXD | Mirrors Bus                |

| BAD               | GOOD              | Protected    | Recessive                | High Impedance (3-state)   |

| GOOD              | BAD               | Protected    | High Impedance           | Recessive (Fail-Safe High) |

#### NOTE

After an undervoltage condition is cleared and the supplies have returned to valid levels, the device typically resumes normal operation in  $300 \mu s$

### 8.3.3.4 Floating Pins

Pullups and pulldowns should be used on critical pins to place the device into known states if the pins float. The TXD pin should be pulled up through a resistor to  $V_{CC1}$  to force a recessive input level if the microprocessor output to the pin floats.

### 8.3.3.5 CAN Bus Short-Circuit Current Limiting

The device has several protection features that limit the short-circuit current when a CAN bus line is shorted. These include driver current limiting (dominant and recessive). The device has TXD dominant state time out to prevent permanent higher short-circuit current of the dominant state during a system fault. During CAN communication the bus switches between dominant and recessive states with the data and control fields bits, thus the short-circuit current may be viewed either as the instantaneous current during each bus state, or as a DC average current. For system current (power supply) and power considerations in the termination resistors and common-mode choke ratings, use the average short-circuit current. Determine the ratio of dominant and recessive bits by the data in the CAN frame plus the following factors of the protocol and PHY that force either recessive or dominant at certain times:

- · Control fields with set bits

- Bit-stuffing

- Interframe space

- TXD dominant time-out (fault case limiting)

These ensure a minimum recessive amount of time on the bus even if the data field contains a high percentage of dominant bits.

#### **NOTE**

The short-circuit current of the bus depends on the ratio of recessive to dominant bits and their respective short-circuit currents. The average short-circuit current may be calculated with the following formula:

$l_{OS(AVG)} = %Transmit \times [(%REC_Bits \times l_{OS(SS)_REC}) + (%DOM_Bits \times l_{OS(SS)_DOM})] + [%Receive \times l_{OS(SS)_REC}]$

#### Where

- I<sub>OS(AVG)</sub> is the average short-circuit current.

- %Transmit is the percentage the node is transmitting CAN messages.

- %Receive is the percentage the node is receiving CAN messages.

- %REC\_Bits is the percentage of recessive bits in the transmitted CAN messages.

- %DOM Bits is the percentage of dominant bits in the transmitted CAN messages.

- I<sub>OS(SS)</sub> REC is the recessive steady state short-circuit current.

- I<sub>OS(SS)</sub> DOM is the dominant steady state short-circuit current.

#### NOTE

Consider the short-circuit current and possible fault cases of the network when sizing the power ratings of the termination resistance and other network components.

#### 8.4 Device Functional Modes

**Table 8. Driver Function Table**

| INPUT              | OUT                 | DDIVEN DUC CTATE    |                  |

|--------------------|---------------------|---------------------|------------------|

| TXD <sup>(1)</sup> | CANH <sup>(1)</sup> | CANL <sup>(1)</sup> | DRIVEN BUS STATE |

| L                  | Н                   | L                   | Dominant         |

| Н                  | Z                   | Z                   | Recessive        |

(1) H = high level, L = low level, Z = common mode (recessive) bias to  $V_{CC}$  / 2. See Figure 23 and Figure 24 for bus state and common mode bias information.

| Table 0 | ) Ro  | coiver | <b>Function</b> | Table   |

|---------|-------|--------|-----------------|---------|

| Tables  | 1. RH | CHIVEI | Function        | I addie |

| DEVICE MODE      | CAN DIFFERENTIAL INPUTS  V <sub>ID</sub> = V <sub>CANH</sub> - V <sub>CANL</sub> | BUS STATE | RXD PIN <sup>(1)</sup> |

|------------------|----------------------------------------------------------------------------------|-----------|------------------------|

|                  | $V_{ID} \ge 0.9 \text{ V}$                                                       | Dominant  | L                      |

| Normal or Silent | $0.5 \text{ V} < \text{V}_{\text{ID}} < 0.9 \text{ V}$                           | ?         | ?                      |

| Normal of Silent | V <sub>ID</sub> ≤ 0.5 V                                                          | Recessive | Н                      |

|                  | Open (V <sub>ID</sub> ≈ 0 V)                                                     | Open      | Н                      |

(1) H = high level, L = low level, ? = indeterminate.

Table 10. Function Table<sup>(1)</sup>

|                  |             | DRIVER |           | RECEIVER                                               |        |           |  |  |

|------------------|-------------|--------|-----------|--------------------------------------------------------|--------|-----------|--|--|

| INPUTS           | UTS OUTPUTS |        | BUS STATE | DIFFERENTIAL INPUTS                                    | OUTPUT | BUS STATE |  |  |

| TXD              | CANH        | CANL   | DUS STATE | V <sub>ID</sub> = CANH-CANL                            | RXD    | BUS STATE |  |  |

| L <sup>(2)</sup> | Н           | L      | DOMINANT  | V <sub>ID</sub> ≥ 0.9 V                                | L      | DOMINANT  |  |  |

| Н                | Z           | Z      | RECESSIVE | $0.5 \text{ V} < \text{V}_{\text{ID}} < 0.9 \text{ V}$ | ?      | ?         |  |  |

| Open             | Z           | Z      | RECESSIVE | V <sub>ID</sub> ≤ 0.5 V                                | Н      | RECESSIVE |  |  |

| X                | Z           | Z      | RECESSIVE | Open                                                   | Н      | RECESSIVE |  |  |

- (1) H = high level; L = low level; X = irrelevant; ? = indeterminate; Z = high impedance

- (2) Logic low pulses to prevent dominant time-out.

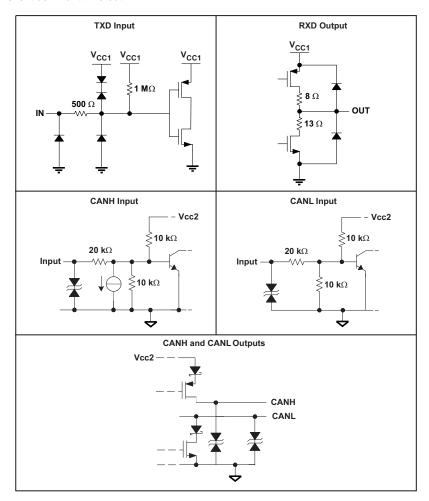

Figure 26. Equivalent I/O Schematics

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

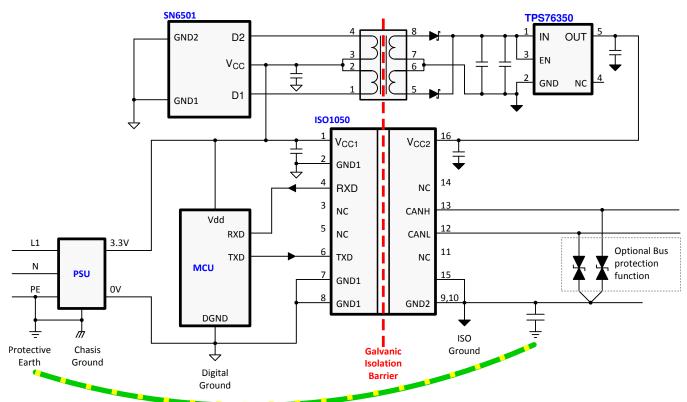

ISO1050 can be used with other components from TI such as a microcontroller, a transformer driver, and a linear voltage regulator to form a fully isolated CAN interface.

## 9.2 Typical Application

Figure 27. Application Circuit

### 9.2.1 Design Requirements

Unlike optocoupler-based solution, which needs several external components to improve performance, provide bias, or limit current, ISO1050 only needs two external bypass capacitors to operate.

### 9.2.2 Detailed Design Procedure

### 9.2.2.1 Bus Loading, Length and Number of Nodes

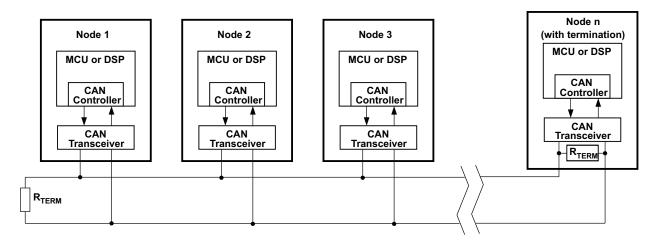

The ISO11898 Standard specifies a maximum bus length of 40 m and maximum stub length of 0.3 m with a maximum of 30 nodes. However, with careful design, users can have longer cables, longer stub lengths, and many more nodes to a bus. A high number of nodes requires a transceiver with high input impedance such as the ISO1050.

### **Typical Application (continued)**

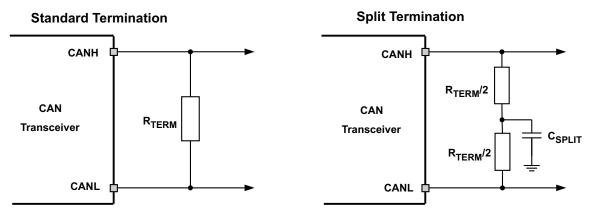

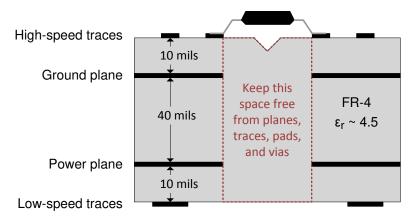

Many CAN organizations and standards have scaled the use of CAN for applications outside the original ISO11898 standard. They have made system level trade offs for data rate, cable length, and parasitic loading of the bus. Examples of some of these specifications are ARINC825, CANopen, CAN Kingdom, DeviceNet and NMEA200.